# 数据手册

Datasheet

BL32F003 系列

32 位基于 ARM Cortex M0 微控制器

## 目录

| 数  | 据手册 | 册              | 1  |

|----|-----|----------------|----|

| 目  | 录   |                | 2  |

| 修  | 订记录 | ₹              | 5  |

| 1. | 简介. |                | 6  |

|    | 1.1 | 概述             | 6  |

|    | 1.2 | 产品特性           | 6  |

| 2. | 芯片组 | 结构框图           | 8  |

| 3. | 引脚  | 定义             | 9  |

|    | 3.1 | 引脚示意图          | 9  |

|    | 3.2 | 引脚定义           | 10 |

|    | 3.3 | 引脚复用功能         | 12 |

| 4. | 功能  | 描述             | 14 |

|    |     | 地址空间映射         |    |

|    | 4.2 | 存储器划分及权限控制     | 14 |

|    |     | 中断向量表          |    |

|    | 4.4 | 系统定时器(SYSTICK) |    |

|    |     | 4.4.1 概述       |    |

|    |     | 4.4.2 特性       |    |

|    |     | 4.4.3 模块结构框图   |    |

|    |     | 4.4.4 功能描述     |    |

|    |     | 4.4.5 寄存器映射    |    |

|    |     | 4.4.6 寄存器描述    |    |

|    | 4.5 | 电源管理           |    |

|    |     | 4.5.1 概述       |    |

|    |     | 4.5.2 特性       |    |

|    |     | 4.5.3 模块结构框图   |    |

|    |     | 4.5.4 功能描述     |    |

|    |     | 4.5.5 寄存器映射    |    |

|    |     | 4.5.6 寄存器描述    |    |

|    | 4.6 | 时钟             |    |

|    |     | 4.6.1 概述       |    |

|    |     | 4.6.2 特性       |    |

|    |     | 4.6.3 模块结构框图   |    |

|    |     | 4.6.4 功能描述     |    |

|    |     | 4.6.5 寄存器映射    | 25 |

|    |     | 4.6.6 寄存器描述    | 26 |

|    | 4.7 | PORTCON        | 30 |

|    |     | 4.7.1 概述       |    |

|    |     | 4.7.2 特性       |    |

|    |     | 4.7.3 模块结构框图   |    |

|    |     | 4.7.4 功能描述     |    |

|    |     | 4.7.5 寄存器映射    | 34 |

| 4.7.6 寄存器描述                | 35  |

|----------------------------|-----|

| 4.8 通用 IO(GPIO)            | 40  |

| 4.8.1 概述                   | 40  |

| 4.8.2 特性                   | 40  |

| 4.8.3 模块结构框图               | 41  |

| 4.8.4 功能描述                 | 41  |

| 4.8.5 寄存器映射                | 43  |

| 4.8.6 寄存器描述                | 43  |

| 4.9 高级定时器(TIMERPLUS)       | 47  |

| 4.9.1 概述                   | 47  |

| 4.9.2 特性                   | 47  |

| 4.9.3 模块结构框图               | 47  |

| 4.9.4 功能描述                 | 48  |

| 4.9.5 寄存器映射                | 52  |

| 4.9.6 寄存器描述                |     |

| 4.10 独立看门狗时钟(IWDT)         |     |

| 4.10.1 概述                  |     |

| 4.10.2 特性                  |     |

| 4.10.3 模块结构框图              |     |

| 4.10.4 功能描述                |     |

| 4.10.5 寄存器映射               | 60  |

| 4.10.6 寄存器描述               | 61  |

| 4.11 基本脉冲宽度调制发生器 (PWMBASE) |     |

| 4.11.1 概述                  |     |

| 4.11.2 特性                  |     |

| 4.11.3 模块结构框图              |     |

| 4.11.4 功能描述                | 63  |

| 4.11.5 寄存器映射               |     |

| 4.11.6 寄存器描述               |     |

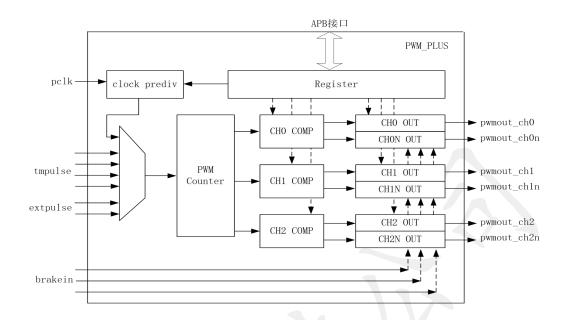

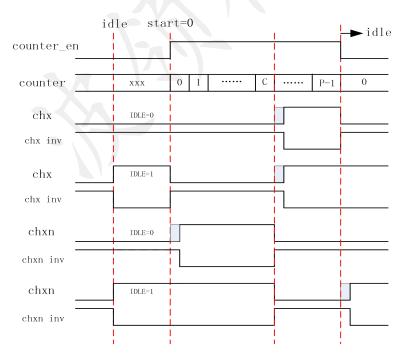

| 4.12 高级脉冲宽度调制发生器(PWMPLUS)  |     |

| 4.12.1 概述                  |     |

| 4.12.2 特性                  |     |

| 4.12.3 模块结构框图              |     |

| 4.12.4 功能描述                |     |

| 4.12.5 寄存器映射               |     |

| 4.12.6 寄存器描述               |     |

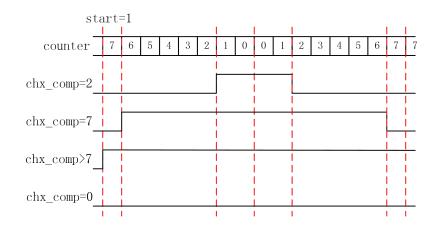

| 4.13 UART 控制器(UART)        |     |

| 4.13.1 概述                  |     |

| 4.13.2 特性                  |     |

| 4.13.3 模块结构框图              |     |

| 4.13.4 功能描述                |     |

| 4.13.5 寄存器映射               |     |

| 4.13.6 寄存器描述               |     |

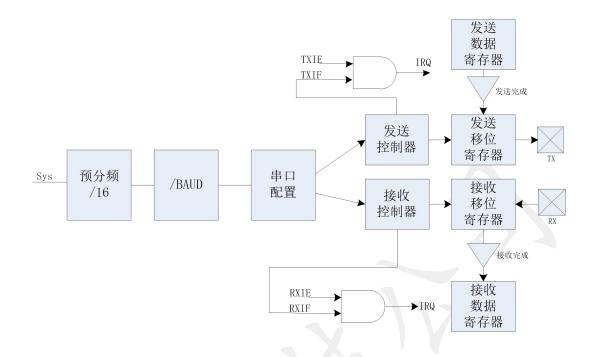

| 4.14 SPI 总线控制器(SPI)        | 100 |

| 4.14.1     | 概述       | .100  |

|------------|----------|-------|

| 4.14.2     | 特性       | .100  |

| 4.14.3     | 模块结构框图   | .101  |

| 4.14.4     | 功能描述     | .101  |

| 4.14.5     | 寄存器映射    | .103  |

| 4.14.6     | 寄存器描述    | .103  |

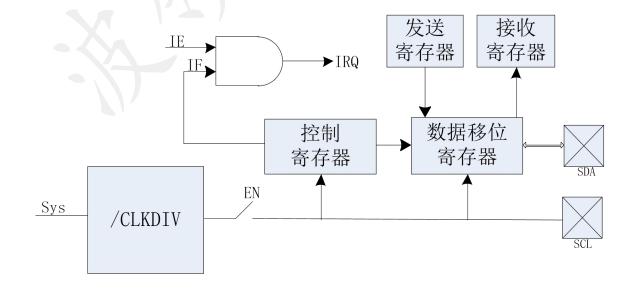

| 4.15 IIC 控 | 制器       | .106  |

| 4.15.1     | 概述       | .106  |

| 4.15.2     | 特性       | .106  |

| 4.15.3     | 模块结构框图   | .106  |

| 4.15.4     | 功能描述     | .107  |

| 4.15.5     | 寄存器映射    | .110  |

| 4.15.6     | 寄存器描述    | .110  |

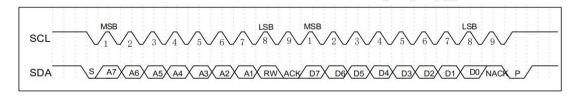

| 4.16 模数等   | 转换器(ADC) | . 113 |

| 4.16.1     | 概述       | .113  |

| 4.16.2     | 特性       | .113  |

| 4.16.3     | 模块结构框图   | .114  |

| 4.16.4     | 功能描述     | .114  |

| 4.16.5     | 寄存器映射    | .115  |

| 4.16.6     | 寄存器描述    | .116  |

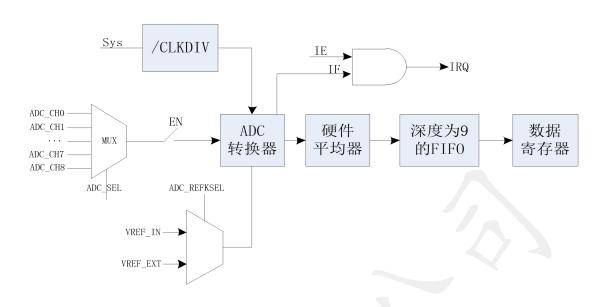

| 4.17 SPIFL | ASH_CTRL | . 124 |

| 4.17.1     | 概述       | .124  |

| 4.17.2     | 特性       | .124  |

| 4.17.3     | 模块结构框图   | .124  |

| 4.17.4     | 功能描述     | .125  |

| 4.17.5     | 寄存器映射    | .126  |

| 4.17.6     | 寄存器描述    | .127  |

| 4.18 CACH  | IE 控制器   | . 130 |

| 4.18.1     | 概述       | .130  |

| 4.18.2     | 特性       | .130  |

| 4.18.3     | 模块结构框图   | .130  |

| 4.18.4     | 功能描述     | .131  |

| 4.18.5     | 寄存器映射    | .131  |

| 4 18 6     | 客存哭描述    | 131   |

## 文档说明

由于版本升级或存在其他原因,本文档内容会不定期进行更新。除非另有约定,本文档内容仅作为使用指导,本文档中的所有陈述、信息和建议不构成任何明示或暗示的担保。

## 修订记录

| 版本  | 日期        | 内容 | 相关文档 |  |  |

|-----|-----------|----|------|--|--|

| 1.0 | 2021.6.30 | 初版 |      |  |  |

|     |           |    |      |  |  |

|     |           |    |      |  |  |

## 1. 简介

### 1.1 概述

BL32F003 内嵌 ARM Cortex M0 内核,最高工作频率可达 48MHz,内置高速存储器,丰富的增强型 IO 端口和外设连接到总线。本产品包括 16 个 IO、1 个 12 位的 ADC (9 通道)、2 个 16 位的高级定时器,具有输入捕获和周期脉冲输出等功能、1 个 32 位的 iWDT、3 路独立的基本 PWM 波形发生器、3 路独立高级 PWM 波形发生器,支持死区和互补功能、1 个 SPI、1 个 IIC、1 个 UART。

本产品系列工作电压为 2.3V~3.6V, 工作温度为-40℃~105℃。多种省电工作模式保证低功耗应用的要求。

本产品提供 QFN20、TSSOP20 的封装形式,后续根据需要还会增加不同的封装形式。 本产品适用于以下应用场合:四轴飞行器、键盘、鼠标、自拍杆、调光灯等产品。

### 1.2 产品特性

- 内核与系统

- 32 位 ARM Cortex M0 处理器内核

- 最高工作频率为 48MHz

- 24位的系统嘀嗒定时器

- 集成嵌套向量中断控制器(NVIC),提供最多 32 个中断

- 通过 SWD 接口烧录程序

- 存储器

- 内置 64K 字节的 FLASH 存储器作为程序存储区

- 内置两块共 3K RAM: 其中一块 2K 作为数据存储区,另一块 1K 作为 cache 的缓存

- 具有 CACHE 功能

- 时钟、复位及电源管理

- 2.3V~3.6V 供电电压

- 上电/断电复位(POR/PDR)、看门狗复位、片外专用引脚复位(EXTRST)

- 内置 4~32MHz 高频晶体振荡驱动器

- 内置经出厂调校的 48MHz 的高频 RC 振荡器

- 内置 32KHz 低频 RC 振荡器

- 低功耗

standby mode, sleep mode, stop mode

- SARADC

- 9 通道 12bit SARADC

- 采样率可以达到 2.4M

- 用于电源电压和外部信号采样

- GPIO

- 最多可达 16 个 IO 口

- 可配置为以下模式: 浮空输入、上拉输入、下拉输入、推挽输出、开漏输出、模拟 IO

- 灵活的中断配置,可配置为电平触发和边沿触发,电平触发可设置为低电平和高电平,边沿触发可设置为上升沿、下降沿和双边沿

- 每个 GPIO 都支持按键唤醒功能,可配置为上升沿唤醒和下降沿唤醒

- 通信接口

- 1个 SPI 接口,可配置主从模式,可编程时钟极性和相位,主模式速率可配置,最高频率为 Fcpu/4,数据传输顺序可配置,读写数据寄存器独立,支持乒乓传输

- 1 个 UART 接口

- 1个 I2C 接口 支持主模式

- 定时器

- 2个16位高级定时器,计数时钟支持1-256分频,具体定时、计数、输入捕获和周期脉冲输出功能,其中一个支持HALL功能

- 1个32位的独立看门狗定时器

- 3路独立的 16 位基本 PWM 波形发生器, 计数时钟支持 1-256 分频, 支持翻转点中断和周期溢出中断

- 3路独立的 16 位高级 PWM 波形发生器, 计数时钟支持 1-256 分频, 支持死区、互补和刹车功能, 支持上升沿计数或下降沿计数, 支持边沿对齐或中心对称波形输出, 支持初始电平、计数起始电平和输出电平取反可配置, 支持翻转点中断、周期溢出中断和特定触发点中断

- 环境

- 工作温度: -40℃~105℃

- 保存温度: -50℃~150℃

- 湿度等级: MSL3

- 封装

- QFN20、TSSOP20

- 应用范围

- 四轴飞行器、键盘、鼠标、自拍杆、调光灯等产品

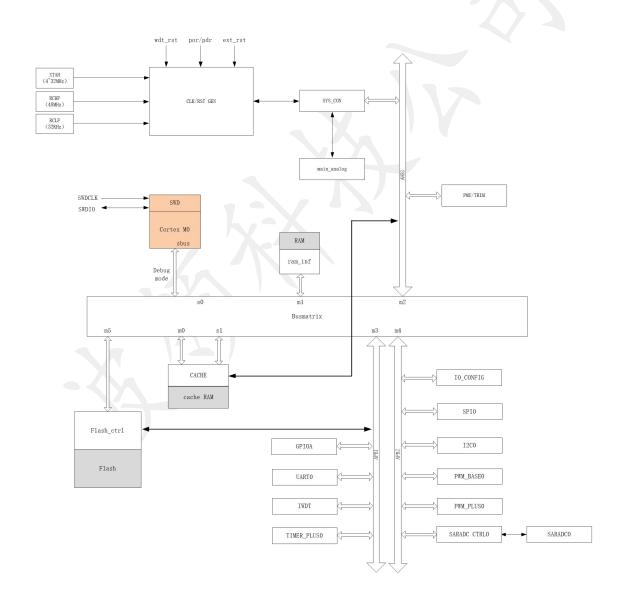

## 2. 芯片结构框图

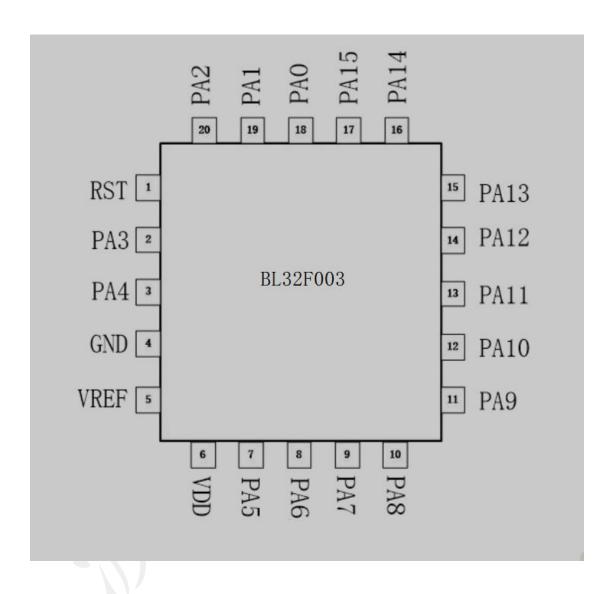

## 3. 引脚定义

## 3.1 引脚示意图

## 3.2 引脚定义

| 引脚 | 引脚                                                                       | 类型  | 复用功能                                                               | 描述                                                                                                                                                                                                  |

|----|--------------------------------------------------------------------------|-----|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 编号 | 定义                                                                       |     |                                                                    |                                                                                                                                                                                                     |

|    | PA0                                                                      | I/O | SPI0_CLK<br>TIMERP0_IN0<br>TIMERP0_OUT0<br>PWMB0_CH0<br>PWMP0_CH0N | PAO: 数字 GPIO 功能引脚<br>SPIO_CLK: SPIO 的时钟引脚<br>TIMERPO_INO: 高级定时器 0 的输入 0 引脚<br>TIMERPO_OUTO: 高级定时器 0 的输出 0 引脚<br>PWMBO_CHO: 基本 PWMO 的通道 0 引脚<br>PWMPO_CHON: 高级 PWMO 的通道 0N 引脚                        |

|    | PA1                                                                      | I/O | SPI0_MOSI<br>UART0_TX<br>HALL_IN0<br>PWMP0_CH1N<br>SARADC_CH1      | PA1:数字 GPIO 功能引脚<br>SPI0_MOSI: SPI0 的主机发送引脚<br>UART0_TX:串口 0 的发送引脚<br>HALL_IN0:霍尔接口的通道 0 引脚<br>PWMP0_CH1N:高级 PWM0 的通道 1N 引脚<br>SARADC_CH1: SARADC 的通道 1 引脚                                          |

|    | PA2                                                                      | I/O | SPI0_MISO UART0_RX HALL_IN1 PWMP0_CH2N SARADC_CH0                  | PA2:数字 GPIO 功能引脚<br>SPI0_MISO:SPI0 的主机接收引脚<br>UART0_RX:串口 0 的接收引脚<br>HALL_IN1:霍尔接口的通道 1 引脚<br>PWMP0_CH2N:高级 PWM0 的通道 2N 引脚<br>SARADC_CH0:SARADC 的通道 0 引脚                                            |

|    | PA3                                                                      | I/O | IIC0_SDA<br>PWMP0_CH0<br>XTAH_IN                                   | PA3:数字 GPIO 功能引脚 IIC0_SDA: IIC0 的数据引脚 PWMP0_CH0:高级 PWM0 的通道 0 引脚 XTAH_IN:高频晶振的输入引脚                                                                                                                  |

|    | PA4                                                                      | I/O | IIC0_SCL<br>PWMP0_CH1<br>XTAH_OUT                                  | PA4: 数字 GPIO 功能引脚<br>IIC0_SCL: IIC0 的时钟引脚<br>PWMP0_CH1: 高级 PWM0 的通道 1 引脚<br>XTAH_OUT: 高频晶振的输出引脚                                                                                                     |

|    | PA5 I/O SPI0_SSN TIMERP0_IN1 TIMERP0_OUT1 PWMB0_CH1 PWMP0_CH2 SARADC_CH7 |     | TIMERPO_IN1 TIMERPO_OUT1 PWMB0_CH1 PWMP0_CH2                       | PA5:数字 GPIO 功能引脚<br>SPIO_SSN:SPIO 的片选引脚<br>TIMERPO_IN1:高级定时器 0 的输入 1 引脚<br>TIMERPO_OUT1:高级定时器 0 的输出 1 引脚<br>PWMBO_CH1:基本 PWMO 的通道 1 引脚<br>PWMPO_CH2:高级 PWMO 的通道 2 引脚<br>SARADC_CH7: SARADC 的通道 7 引脚 |

| PA6  | I/O | IIC0_SDA<br>BRAKE_IN0<br>SARADC_CH6                               | PA6:数字 GPIO 功能引脚 IIC0_SDA: IIC0 的数据引脚 BRAKE_IN0:刹车输入 0 通道 SARADC_CH6: SARADC 的通道 6 引脚                                                                                                     |

|------|-----|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA7  | I/O | IIC0_SCL<br>BRAKE_IN1<br>HALL_IN2<br>SARADC_CH5                   | PA7: 数字 GPIO 功能引脚 IIC0_SCL: IIC0 的时钟引脚 BRAKE_IN1: 刹车输入 1 通道 HALL_IN2: 霍尔接口的通道 2 引脚 SARADC_CH5: SARADC 的通道 5 引脚                                                                            |

| PA8  | I/O | UART0_TX TIMERP0_IN0 TIMERP0_OUT0 PWMP0_CH2 PWMP0_CH0N            | PA8:数字 GPIO 功能引脚 UART0_TX:串口0的发送引脚 TIMERP0_IN0:高级定时器0的输入0引脚 TIMERP0_OUT0:高级定时器0的输出0引脚 PWMP0_CH2:高级PWM0的通道0引脚 PWMP0_CH0N:高级PWM0的通道0N引脚                                                     |

| PA9  | I/O | UARTO_RX TIMERPO_IN1 TIMERPO_OUT1 PWMBO_CH2 PWMPO_CH1N SARADC_CH4 | PA9: 数字 GPIO 功能引脚 UART0_RX: 串口 0 的接收引脚 TIMERP0_IN1: 高级定时器 0 的输入 1 引脚 TIMERP0_OUT1: 高级定时器 0 的输出 1 引脚 PWMB0_CH2: 基本 PWM0 的通道 2 引脚 PWMP0_CH1N: 高级 PWM0 的通道 1N 引脚 SARADC_CH4: SARADC 的通道 4 引脚 |

| PA10 | I/O | SPI0_CLK TIMERP0_IN0 TIMERP0_OUT0 PWMB0_CH0 PWMP0_CH2N            | PA10:数字 GPIO 功能引脚<br>SPI0_CLK:SPI0 的时钟引脚<br>TIMERP0_IN0:高级定时器 0 的输入 0 引脚<br>TIMERP0_OUT0:高级定时器 0 的输出 0 引脚<br>PWMB0_CH0:基本 PWM0 的通道 0 引脚<br>PWMP0_CH2N:高级 PWM0 的通道 2N 引脚                   |

| PA11 | I/O | SPI0_MOSI<br>TIMERP0_IN1<br>TIMERP0_OUT1<br>PWMP0_CH0             | PA11:数字 GPIO 功能引脚<br>SPI0_MOSI: SPI0 的主机发送引脚<br>TIMERP0_IN1:高级定时器 0 的输入 1 引脚<br>TIMERP0_OUT1:高级定时器 0 的输出 1 引脚<br>PWMP0_CH0:高级 PWM0 的通道 0 引脚                                               |

| PA12 | I/O | SPI0_ MISO<br>TIMERP0_IN0<br>TIMERP0_OUT0<br>PWMP0_CH1            | PA12:数字 GPIO 功能引脚<br>SPI0_MISO:SPI0 的主机接收引脚<br>TIMERP0_IN0:高级定时器 0 的输入 0 引脚<br>TIMERP0_OUT0:高级定时器 0 的输出 0 引脚<br>PWMP0_CH1:高级 PWM0 的通道 1 引脚                                                |

| PA13 | I/O | SWCLK<br>PWMP0_CH2                                                | PA13:数字 GPIO 功能引脚<br>SWCLK:SW 下载口的时钟引脚<br>PWMP0_CH2:高级 PWM0 的通道 2 引脚                                                                                                                      |

| PA | A14 I/O | SWDIO<br>TIMERP0_IN1<br>TIMERP0_OUT1<br>PWMB0_CH1<br>SARADC_CH3    | PA14:数字 GPIO 功能引脚<br>SWDIO:SW下载口的数据引脚<br>TIMERP0_IN1:高级定时器 0 的输入 1 引脚<br>TIMERP0_OUT1:高级定时器 0 的输出 1 引脚<br>PWMB0_CH1:基本 PWM0 的通道 1 引脚<br>SARADC_CH3:SARADC 的通道 3 引脚     |

|----|---------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA | A15 I/O | SPI0_SSN<br>TIMERP0_IN0<br>TIMERP0_OUT0<br>PWMB0_CH2<br>SARADC_CH2 | PA15:数字 GPIO 功能引脚<br>SPI0_SSN:SPI0 的片选引脚<br>TIMERP0_IN0:高级定时器 0 的输入 0 引脚<br>TIMERP0_OUT0:高级定时器 0 的输出 0 引脚<br>PWMB0_CH2:基本 PWM0 的通道 2 引脚<br>SARADC_CH2: SARADC 的通道 2 引脚 |

## 3.3 引脚复用功能

| 引脚名称 | SEL000              | SEL001 | SEL010  | SEL011  | SEL100 | SEL101 | SEL111                                                                            |  |      |

|------|---------------------|--------|---------|---------|--------|--------|-----------------------------------------------------------------------------------|--|------|

| DAO  | CDIOAO              | SPI0   | TIMERP0 | TIMERP0 | PWMB0  | PWMP0  |                                                                                   |  |      |

| PA0  | GPIOA0              | _CLK   | _IN0    | _OUT0   | _CH0   | _CH0N  | SEL111  SARADC _CH1 SARADC _CH0 XTAH _IN XTAH _OUT SARADC _CH7 SARADC _CH6 SARADC |  |      |

| PA1  | GPIOA1              | SPI0   | UART0   | HALL    | PWMP0  |        | SARADC                                                                            |  |      |

| PAI  | GPIOAT              | _MOSI  | _TX     | _IN0    | _CH1N  |        | _CH1                                                                              |  |      |

| PA2  | GPIOA2              | SPI0   | UART0   | HALL    | PWMP0  |        | SARADC                                                                            |  |      |

| TAZ  | GFIOA2              | _MISO  | _RX     | _IN1    | _CH2N  |        | _CH0                                                                              |  |      |

| PA3  | GPIOA3              | I2C0   | PWMP0   |         |        |        |                                                                                   |  | ХТАН |

| TAS  |                     | _SDA   | _CH0    |         |        | _IN    |                                                                                   |  |      |

| PA4  | GPIOA4              | I2C0   | PWMP0   |         |        |        | ХТАН                                                                              |  |      |

| IAT  |                     | _SCL   | _CH1    |         |        |        | _OUT                                                                              |  |      |

| PA5  | GPIOA5              | SPI0   | TIMERP0 | TIMERP0 | PWMB0  | PWMP0  | SARADC                                                                            |  |      |

| 1713 |                     | _SSN   | _IN1    | _OUT1   | _CH1   | _CH2   | _CH7                                                                              |  |      |

| PA6  | GPIOA6              | I2C0   |         | BREAK   |        |        | SARADC                                                                            |  |      |

| 1710 | Grioao              | _SDA   |         | _IN0    |        |        | _CH6                                                                              |  |      |

| PA7  | GPIOA7 I2C0<br>_SCL | I2C0   | BREAK   | HALL    |        |        | SARADC                                                                            |  |      |

| PA/  |                     | _SCL   | _IN1    | _IN2    |        |        | _CH5                                                                              |  |      |

| PA8        | GPIOA8       | UART0       | TIMERP0    | TIMERP0    | PWMP0      | PWMP0      |            |            |            |           |                  |         |         |       |  |        |

|------------|--------------|-------------|------------|------------|------------|------------|------------|------------|------------|-----------|------------------|---------|---------|-------|--|--------|

| TAO GITOAO |              | _TX         | _IN0       | _OUT0      | _CH2       | _CH0N      |            |            |            |           |                  |         |         |       |  |        |

| PA9        | GPIOA9       | UART0       | TIMERP0    | TIMERP0    | PWMB0      | PWMP0      | SARADC     |            |            |           |                  |         |         |       |  |        |

| PA9        | GPIOA9       | _RX         | _IN1       | _OUT1      | _CH2       | _CH1N      | _CH4       |            |            |           |                  |         |         |       |  |        |

| PA10       | GPIOA10      | SPI0        | TIMERP0    | TIMERP0    | PWMB0      | PWMP0      |            |            |            |           |                  |         |         |       |  |        |

| PAIU       | GPIOATO      | _CLK        | _IN0       | _OUT0      | _CH0       | _CH2N      |            |            |            |           |                  |         |         |       |  |        |

| DA 11      | GPIOA11      | CDIO A 11   | SPI0       | TIMERP0    | TIMERP0    | PWMP0      |            |            |            |           |                  |         |         |       |  |        |

| PA11       |              | _MOSI       | _IN1       | _OUT1      | _CH0       |            |            |            |            |           |                  |         |         |       |  |        |

| DA 12      | GPIOA12      | SPI0        | TIMERP0    | TIMERP0    | PWMP0      |            |            |            |            |           |                  |         |         |       |  |        |

| PA12       |              | _MISO       | _IN0       | _OUT0      | _CH1       | -          |            |            |            |           |                  |         |         |       |  |        |

| DA 12      | CDIO A 12    | SWCLK       | PWMP0      |            |            |            |            |            |            |           |                  |         |         |       |  |        |

| PA13       | GPIOA13      | SWCLK       | _CH2       |            | 77         | <b>—</b>   |            |            |            |           |                  |         |         |       |  |        |

| DA 14      | GPIOA14      | CDV C . 1.4 | CDIO A 1.4 | CDIO A 1 4 | CDIO A 1.4 | CDIO A 1.4 | CDIO A 14 | CDIO A 1.4 GWDIO | TIMERP0 | TIMERP0 | PWMB0 |  | SARADC |

| PA14       |              | SWDIO       | _IN1       | _OUT1      | _CH1       |            | _CH3       |            |            |           |                  |         |         |       |  |        |

| DA 15      | PA15 GPIOA15 | SPI0        | TIMERP0    | TIMERP0    | PWMB0      |            | SARADC     |            |            |           |                  |         |         |       |  |        |

| PAIS       |              | _SSN        | _IN0       | _OUT0      | _CH2       |            | _CH2       |            |            |           |                  |         |         |       |  |        |

## 4. 功能描述

### 4.1 地址空间映射

BL32F003 控制器为 32 位通用控制器,提供了 4G 字节的寻址空间,如下表所示。数据格式 仅支持小端模式,各模块具体寄存器排布及操作说明在后面章节有详细的描述。

| 起始         | 结束         | 模块          |

|------------|------------|-------------|

| 存储器        |            |             |

| 0x00000000 | 0x0000FFFF | CACHE CODE  |

| 0x20000000 | 0x200007FF | RAM         |

| 0x41000000 | 0x4100FFFF | FLASH DATA  |

| AHB 总线外设   |            |             |

| 0x40000000 | 0x400007FF | SYSCON      |

| 0x40000800 | 0x40000FFF | PMU         |

| 0x40002000 | 0x400027FF | CACHE       |

| APB1 总线外设  |            |             |

| 0x40060000 | 0x400607FF | GPIOA       |

| 0x40067000 | 0x400677FF | TIMER_PLUS0 |

| 0x4006A000 | 0x4006A7FF | IWDT        |

| 0x4006B000 | 0x4006B7FF | UART0       |

| 0x4006F000 | 0x4006F7FF | FLASH_CTRL  |

| APB2 总线外设  |            |             |

| 0x400B0000 | 0x400B07FF | IO_CONFIG   |

| 0x400B1000 | 0x400B17FF | PWM_BASE0   |

| 0x400B4000 | 0x400B47FF | PWM_PLUS0   |

| 0x400B8000 | 0x400B87FF | SPI0        |

| 0x400B9000 | 0x400B97FF | I2C0        |

| 0x400BA000 | 0x400BA7FF | SARADC0     |

## 4.2 存储器划分及权限控制

本芯片具有外置 flash 程序存储器,最大支持 64KB 字节容量和 3K 数据存储器 RAM。 最低 4K 空间支持屏蔽,我司的 boot 程序放在该 4K 空间内,主要用于 trim 值的保存,

上电后读出 trim 值并保存到相应的寄存器中,以及一些 boot 程序函数库等。

3K 的 RAM 在物理上共有两块: 一块 1K 的 RAM 作为 CACHE 的缓存区,另一块 2K 的 RAM 作为芯片的数据区。

## 4.3 中断向量表

中断向量表如下:

表 1 BL32F003 中断向量表

| 72.1 | DL321003 平断同重农  |

|------|-----------------|

| 中断源  | 外设中断            |

| 0    | UART0_IRQn      |

| 1    | TIMERPLUS0_IRQn |

| 2    | PWMBASE0_IRQn   |

| 3    | PWMPLUS0_IRQn   |

| 4    | IIC0_IRQn       |

| 5    | SARADC_IRQn     |

| 6    | SPI0_IRQn       |

| 7    | IIWDT_IRQn      |

| 8    | GPIOA0_IRQn     |

| 9    | GPIOA1_IRQn     |

| 10   | GPIOA2_IRQn     |

| 11   | GPIOA3_IRQn     |

| 12   | GPIOA4_IRQn     |

| 13   | GPIOA5_IRQn     |

| 14   | GPIOA6_IRQn     |

| 15   | GPIOA7_IRQn     |

| 16   | GPIOA8_IRQn     |

| 17   | GPIOA9_IRQn     |

| 18   | GPIOA10_IRQn    |

| 19   | GPIOA11_IRQn    |

| 20   | GPIOA12_IRQn    |

| 21   | GPIOA13_IRQn    |

| 22   | GPIOA14_IRQn    |

| 23   | GPIOA15_IRQn    |

| L    |                 |

## 4.4 系统定时器(SYSTICK)

### 4.4.1 概述

CortexT<sup>M</sup>-M0 核内部提供了一个 24 位系统定时器。该定时器使能后装载当前值寄存器(SYST\_VAL)内数值并向下递减至 0,并在下个时钟沿重新加载重载寄存器(SYST\_LOAD)内数值。计数器再次递减至 0 时,计数器状态寄存器(SYST\_CTRL)中标识位 COUNTFLAG 置位,读该位可清零。

复位后,SYST\_VAL 寄存器与 SYST\_LOAD 寄存器值均未知,因此使用前需初始化,向 SYST\_VAL 写入任意值,清零同时复位状态寄存器,保证装载值为 SYST\_LOAD 寄存器中数值。

当 SYST LOAD 寄存器值为 0 时,重新装载后计时器保持为 0,并停止重新装载。

### 4.4.2 特性

- 24 位系统定时器

- 递减

- 写清零

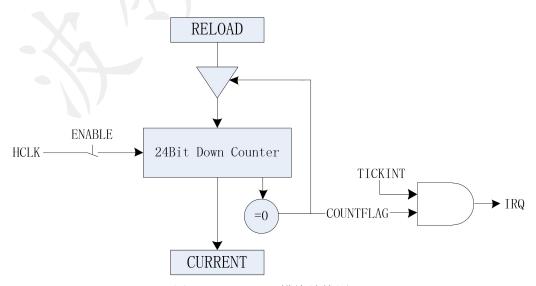

### 4.4.3 模块结构框图

图 5-4-1 Systick 模块结构图

## 4.4.4 功能描述

该定时器使能后,装载当前值寄存器(SYST\_VAL)内数值并向下递减至 0,并在下个时钟重新加载重载寄存器(SYST\_LOAD)内数值。计数器再次递减至 0 时,计数器状态寄存器(SYST CTRL)中的 标志位 COUNTFLAG 置位,读该位可清零。

复位后,SYST\_VAL 寄存器与 SYST\_LOAD 寄存器值均未知,因此使用前需初始化,向 SYST\_VAL 写入任意值,清零同时复位状态寄存器,保证装载值为 SYST\_LOAD 寄存器中数值。

当 SYST\_LOAD 寄存器值为 0 时,重新装载后计时器保持为 0,并停止重新装载。 该计数器可用作实时系统的滴答定时器或一个简单的计数器。

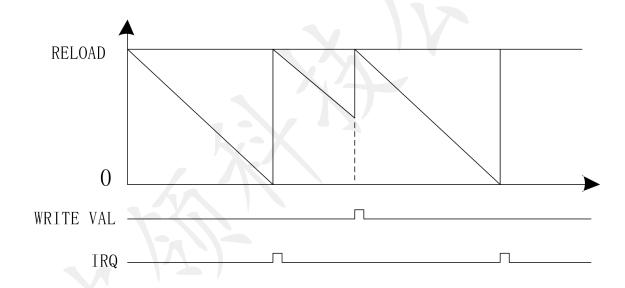

SysTick 计数时序图如图 5-4-2 所示。

图 5-4-2 systick 计数时序图

## 4.4.5 寄存器映射

| 名称        | 偏移                      | 类型  | 复位值  | 描述     |  |  |  |

|-----------|-------------------------|-----|------|--------|--|--|--|

| SYSTICK   | SYSTICK BASE:0xE000E010 |     |      |        |  |  |  |

| SYST_CTRL | 0x00                    | R/W | 0x00 | 状态寄存器  |  |  |  |

| SYST_LOAD | 0x04                    | R/W | 0x00 | 重载寄存器  |  |  |  |

| SYST_VAL  | 0x08                    | R/W | 0x00 | 当前值寄存器 |  |  |  |

## 4.4.6 寄存器描述

#### SYST\_CTRL 状态寄存器 (0x00)

| 位域    | 名称        | 类型  | 复位值 | 描述             |

|-------|-----------|-----|-----|----------------|

| 31:17 | RESERVED  | R   | 0   | 保留位            |

| 16    | COUNTFLAG | R   | 0   | 计数器计数到 0,此位置 1 |

| 15:2  | RESERVED  | R   | 0   | 保留位            |

| 1     | TINKINT   | R/W | 0   | 中断使能位          |

|       |           |     |     | 0: 禁能          |

|       |           |     |     | 1: 使能          |

| 0     | ENABLE    | R/W | 0   | 定时器使能位         |

|       |           |     |     | 0: 禁能          |

|       |           |     |     | 1: 使能          |

#### SYST\_LOAD 重载寄存器(0x04)

| 位域    | 名称       | 类型  | 复位值 | 描述                   |

|-------|----------|-----|-----|----------------------|

| 31:24 | RESERVED | R   | 0   | 保留位                  |

| 23:0  | RELOAD   | R/W | 0   | 计数器计数到0加载本寄存器的值,重新开始 |

|       |          | )   |     | 计数                   |

#### SYST\_VAL 当前值寄存器 (0x08)

| 位域    | 名称       | 类型  | 复位值 | 描述                   |

|-------|----------|-----|-----|----------------------|

| 31:24 | RESERVED | R   | 0   | 保留位                  |

| 23:0  | VAL      | R/W | 0   | 读操作返回当前计数值,写操作会清零该寄存 |

|       |          |     |     | 器,同时清除 COUNTFLAG 标志位 |

### 4.5 电源管理

## 4.5.1 概述

BL32F003 芯片提供多种低功耗模式满足客户的不同需求。

### 4.5.2 特性

- 工作电压是 2.3V-3.6V

- ADC 采用单独的电源供电和参考电源

- ADC 内部有一个 1.4V 的参考源

- 上电复位 (POR) 和掉电复位(PDR)

- 外部上电复位引脚

- 低功耗模式有:正常工作模式(normal)、暂停模式(standby)、休眠模式(sleep)、 停止模式(stop)

## 4.5.3 模块结构框图

### 4.5.4 功能描述

#### 电源

BL32F003 芯片的工作电压是 2.3V-3.6V。内置电压调节器提供 1.2V 的电源给内部数字电路。为了提高转换精度,ADC 采用单独的电源供电和参考电源,ADC 内部有一个 1.4V 的参考源,内部参考源和外部参考源只能选择一个,如果选择内部参考源,则外部参考引脚必须悬空。

#### 上电复位(POR)和掉电复位(PDR)

当 VDD/VDDA 的电压低于一个规定门限时,器件维持复位状态,而无需外部复位电路。 有关上电与掉电复位的电压门限请参考数据手册的电气特性章节内容。

#### 低功耗模式

低功耗模式有:正常工作模式(normal)、暂停模式(standby)、休眠模式(sleep)、 停止模式(stop)。

正常工作模式: 芯片完成上电并且 POR 释放后,RCHF 时钟正常产生输出(上电默认时钟频率是 24MHz),数字电路可以正常工作,CPU 开始进行正常取值,程序正常运行。

暂停模式(standby:数字不掉电,系统时钟停止,用RCHF作为唤醒时钟):在正常工作模式下,当配置STANDBY\_MODE寄存器为1后,芯片进入暂停模式。此时,模拟电路将不发生变化,供电和时钟不变。仅将CPU和外设时钟关掉,唤醒电路还是由RCHF作为唤醒时钟。STANDBY模式可通过外部IO信号唤醒,PMU检测到相应信号后,将STANDBY\_MODE信号清为0,表示退出暂停模式,回到正常工作模式。该模式下唤醒时间小于5us。

休眠模式(sleep:数字不掉电,系统时钟停止):正常工作模式下,当配置 SLEEP\_MODE 寄存器为 1 后,芯片进入休眠模式。此时,模拟电路将功耗消耗比较大的模拟模块全部关闭,只保留 BG、LP\_LDO 和 RCLF(32K 时钟),数字电源域由 LP\_LDO 供电,系统时钟由于 RCHF 关闭而停止,此时整个数字电路只有 PMU、RTC 和 IWDT 工作在 RCLF 下,其他所有数字电路由于没有时钟而停止。SLEEP 模式可通过外部 IO 信号唤醒,PMU 检测到相应信号后,将 SLEEP\_MODE 信号清为 0,表示退出停止模式,模拟电路检测到 SLEEP\_MODE 为 0 后,将主 LDO 打开,并且将 RCHF 打开,从而使得数字电路恢复时钟正常工作。

停止模式(Stop: 1.2V 电源关闭): 正常工作模式下,当配置 STOP\_MODE 寄存器为 1后,芯片进入停止模式。此时,所有的 LDO 全部关闭,所有 1.2V 下数字电路全部掉电,所有的 3.3V 电源域下的模拟模块全部关闭,只保留极少部分的模拟唤醒电路在工作。该模式下只有 IO 可以作为唤醒信号,当外部 IO 唤醒信号到来时,模拟唤醒电路检测到相应唤醒信号后,开启 BG、LDO、RCHF等所有电路,使芯片重新上电,进入正常工作模式。

此外在正常工作模式下,还可以通过降低系统时钟频率和关闭未用到的外设时钟来降低功耗。

## 4.5.5 寄存器映射

| 名称                  | 偏移   | 类型  | 复位值  | 描述                  |  |  |  |

|---------------------|------|-----|------|---------------------|--|--|--|

| PMU BASE:0x40000800 |      |     |      |                     |  |  |  |

| LPOW_MD             | 0x00 | R/W | 0x00 | 低功耗模式选择寄存器          |  |  |  |

| LPMD_WKEN           | 0x04 | R/W | 0x00 | 低功耗唤醒源使能寄存器         |  |  |  |

| LPMD_WKST           | 0x08 | R/W | 0x00 | 低功耗唤醒源状态寄存器         |  |  |  |

| TRIM_POW            | 0x20 | R/W | 0x00 | POW 相关模拟模块 TRIM 寄存器 |  |  |  |

| TRIM_RC             | 0x24 | R/W | 0x00 | RC 时钟模块 TRIM 寄存器    |  |  |  |

| TRIM_LOCK           | 0x28 | R/W | 0x00 | TRIM 锁定寄存器          |  |  |  |

## 4.5.6 寄存器描述

#### LPOW\_MD 寄存器(0x00)

| 位域   | 名称        | 类型          | 复位值 | 描述                       |

|------|-----------|-------------|-----|--------------------------|

| 31:4 | RESERVED  | R           | 0   | 保留位                      |

| 2    | CTOR      | D/W/        |     | 向该寄存器写 1,芯片进入 STOP 模式    |

| 3    | STOP      | R/W         | 0   | 软件写 1, 硬件自动清零            |

| 2    | RESERVED  | R/W         | 0   | 保留位                      |

| 1    | CLEED     | D/W/        | 0   | 向该寄存器写 1, 芯片进入 SLEEP 模式  |

|      | SLEEP     | R/W         |     | 软件写1,硬件自动清零              |

|      | O CTANDDY | STANDBY R/W | 0   | 向该寄存器写 1,芯片进入 STANDBY 模式 |

| 0    | STANDBY   |             | 0   | 软件写 1, 硬件自动清零            |

注:芯片从正常工作模式进入低功耗模式,每次只能进入一种低功耗模式,唤醒后将从该低功耗模式退出回到正常工作模式,由软件再配置进入另一种低功耗模式。

#### LPMD\_WKEN 寄存器(0x04)

| 位域   | 名称       | 类型   | 复位值 | 描述                     |

|------|----------|------|-----|------------------------|

| 31:3 | RESERVED | R    | 0   | 保留位                    |

|      |          |      |     | 低功耗模式下,IO 唤醒使能         |

|      | lo wwen  | R/W  | 0   | 0: 禁能 1: 使能            |

| 2    | IO_WKEN  | IN W |     | 注 1: 具体哪个 IO 具有唤醒功能可通过 |

|      |          |      |     | PORTA_WKE 寄存器进行配置      |

| 1: 0 | RESERVED | R    | 0   | 预留                     |

#### LPMD\_WKST 寄存器(0x08)

| 位域   | 名称            | 类型   | 复位值         | 描述             |

|------|---------------|------|-------------|----------------|

| 31:3 | RESERVED      | R    | 0           | 保留位            |

|      |               |      | 0           | 低功耗模式下,IO 唤醒标志 |

|      | 2 IO_WKST R/W | D/W/ |             | 1: 发生 IO 事件唤醒  |

| 2    |               | K/W  |             | 0: 未发生 IO 事件唤醒 |

|      |               |      | 硬件置1,软件写1清除 |                |

| 1: 0 | RESERVED      | R    | 0           | 预留             |

### TRIM\_POW 寄存器(0x20)

| 位域    | 名称       | 类型  | 复位值 | 描述                                                          |

|-------|----------|-----|-----|-------------------------------------------------------------|

| 31:25 | RESERVED | R   | 0   | 保留位                                                         |

| 24:23 | TRIM_UVF | R/W | 0   | Uvlo 下降电压选择<br>00: 2.4V<br>01: 2.3V<br>10: 2.1V<br>11: 2.0V |

| 22    | TRIM_HPLD O_H     | R/W | 0 | HPLDO 电压调整到 1.264v<br>0: 不变<br>1: 向上调整到 1.264v                                                                                         |

|-------|-------------------|-----|---|----------------------------------------------------------------------------------------------------------------------------------------|

| 21:20 | TRIM_LPLD O       | R/W | 0 | LPLDO 电压输出 trim 位 00: 1.1V 01: 1.0V 10: 0.9V 11: 0.8V                                                                                  |

| 19    | TRIM_PD_U<br>VLO  | R/W | 0 | UVLO33 trim 位 0: 在 SLEEP 下,电源电压掉至 1.8V 时,芯片复位;此情况下模拟电路会额外消耗 0.6uA 的功耗; 1: 在 SLEEP 下,电源电压掉至 1.3V (+-500mV 的偏差)时,芯片复位;模拟电路会节省 0.6uA 的功耗; |

| 18:16 | TRIM_TEMP CO_HPBG | R/W | 0 | HPBG 温度 trim 位                                                                                                                         |

| 15:12 | TRIM_I_HP         | R/W | 0 | HPBG 电流 trim 位                                                                                                                         |

| 11:8  | TRIM_V_HP         | R/W | 0 | HPBG 电压 trim 位                                                                                                                         |

| 7:4   | TRIM_V_LP         | R/W | 0 | LPBG 电压 trim 位                                                                                                                         |

| 3:0   | TRIM_TEMP CO_LPBG | R/W | 0 | LPBG 温度 trim 位                                                                                                                         |

该 trim 寄存器值可在芯片上电后 BOOT 程序读取相应数据后直接写入相对应的寄存器中,写入后立刻生效。

#### TRIM\_RC 寄存器(0x24)

| 位域    | 名称        | 类型  | 复位值    | 描述               |

|-------|-----------|-----|--------|------------------|

| 31    | RESERVED  | R   | 0      | 保留位              |

| 30:28 | TRIM_CS   | R/W | 3'b100 | RCLF CS trim 位   |

| 27:24 | TRIM_FINE | R/W | 0      | RCLF FINE trim 位 |

| 23:20 | TRIM_N   | R/W | 0 | RCHF N trim 位 |

|-------|----------|-----|---|---------------|

| 19:16 | TRIM_P   | R/W | 0 | RCHF P trim 位 |

| 15:0  | RESERVED | R   | 0 | 保留位           |

该 trim 寄存器值可在芯片上电后 BOOT 程序读取相应数据后直接写入相对应的寄存器中,写入后立刻生效。

#### TRIM\_LOCK 寄存器(0x28)

| 位域   | 名称          | 类型 | 复位值 | 描述                                 |

|------|-------------|----|-----|------------------------------------|

| 31:8 | RESERVED    | R  | 0   | 保留位                                |

| 7:0  | 0 TRIM LOCK | W  | 0   | 将该寄存器写入 0x55 后, TRIM_POW 和 TRIM_RC |

| ,    |             |    |     | 不能被改写,用于保护对 TRIM 寄存器的误改写。          |

### 4.6 时钟

### 4.6.1 概述

系统管理为整个芯片提供时钟源,包括系统时钟和所有外围设备时钟。该控制器还可以 通过单独的外设时钟的开或关,时钟源的选择来进行功耗控制。

## 4.6.2 特性

- 时钟控制

- 每个外设都有单独的开关

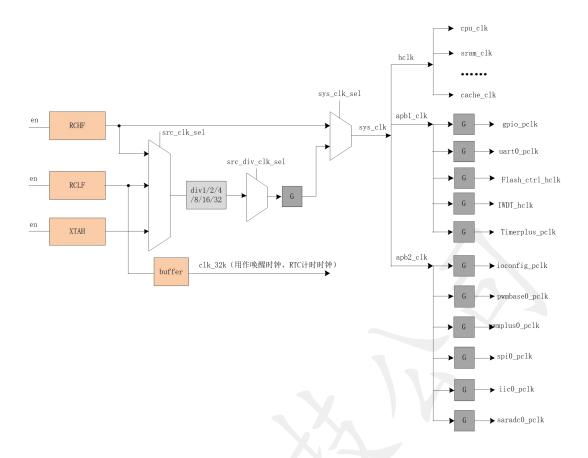

### 4.6.3 模块结构框图

本芯片共有 3 个时钟源: XTAH(4~32MHz 晶体振荡器)、RCHF(24/48MHz RC 振荡器)、RCLF(32KHz RC 振荡器)。

芯片时钟结构图如下:

### 4.6.4 功能描述

系统时钟可以选择 RCHF 或者分频时钟,分频时钟分频系数从 1 到 32,分频时钟来源如下: RCHF、RCLF、XTAH。

当需要改变 DIV\_CLK\_SEL 或 SRC\_CLK\_SEL 寄存器时,需要先将系统时钟切换至 RCHF,然后将该寄存器置为 0,使 DIV\_CLK 关闭,最后再改变 DIV\_CLK\_SEL 或 SRC CLK SEL 的值,从而保证时钟的可靠性。

如果使用 XTAH 时,需要将 XTAL 使能,至少需要等待 2ms 再使用。IWDT 时钟来源可以选择 RCLF 和系统时钟。ADC 采样时钟可以选择系统时钟的 1、2、4、8 分频。

通过 IWDT\_RST\_ST 可以判断出当前复位是上电复位还是 IWDT 复位。

## 4.6.5 寄存器映射

| 名称           | 偏移量                    | 类型  | 复位值 | 描述      |  |  |  |

|--------------|------------------------|-----|-----|---------|--|--|--|

| SYSCON BASE: | YSCON BASE: 0x40000000 |     |     |         |  |  |  |

| CLK_SEL      | 0x00                   | R/W | 0   | 时钟选择寄存器 |  |  |  |

| DIV_CLK_GATE | 0x04  | R/W | 0 | 分频时钟门控寄存器     |

|--------------|-------|-----|---|---------------|

| DEV_CLK_GATE | 0x08  | R/W | 0 | 外设时钟门控寄存器     |

| CHIP_RST_ST  | 0x10  | R/W | 0 | 芯片复位状态寄存器     |

| RC_CON       | 0x100 | R/W | 0 | RC 振荡器时钟控制寄存器 |

| XT_CON       | 0x104 | R/W | 0 | 晶振时钟控制寄存器     |

## 4.6.6 寄存器描述

#### CLK\_SEL 寄存器(0x00)

| 位域    | 名称                      | 类型  | 复位值 | 描述                                                                                                                                               |

|-------|-------------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:12 | RESERVED                | R   | 0   | 保留位                                                                                                                                              |

| 11:10 | SARADC_SMP<br>L_CLK_SEL | R/W | 0   | SARADC 采样时钟选择<br>00: 系统时钟的 1 分频<br>01: 系统时钟的 2 分频<br>10: 系统时钟的 4 分频<br>11: 系统时钟的 8 分频                                                            |

| 9: 7  | RESERVED                | R   | 0   | 保留位                                                                                                                                              |

| 6:4   | SRC_CLK_SEL             | R/W | 0   | 源时钟(SRC_CLK)选择 000: RCHF 001: RCLF 010: XTAH 其他: 保留                                                                                              |

| 3:1   | DIV_CLK_SEL             | R/W | 01  | 分频时钟(DIV_CLK)选择 000: SRC_CLK 的 1 分频 001: SRC_CLK 的 2 分频 010: SRC_CLK 的 4 分频 011: SRC_CLK 的 8 分频 100: SRC_CLK 的 16 分频 101: SRC_CLK 的 32 分频 其他: 保留 |

| 0     | SYS_CLK_SEL             | R/W | 0   | 系统时钟选择<br>0: RCHF 时钟<br>1: DIV_CLK 时钟                                                                                                            |

### DIV\_CLK\_GATE 寄存器(0x04)

| 位域   | 名称               | 类型  | 复位值 | 描述                                                                                                                                                             |

|------|------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:1 | RESERVED         | R   | 0   | 保留位                                                                                                                                                            |

| 0    | DIV_CLK_G<br>ATE | R/W |     | 分频时钟门控 1: 分频时钟输出 0: 分频时钟禁止 注: 当需要改变 DIV_CLK_SEL 或 SRC_CLK_SEL 寄存器时,需要先将系统时钟切换至 RCHF,然 后将该寄存器置为 0,使 DIV_CLK 关闭,最后再 改变 DIV_CLK_SEL 或 SRC_CLK_SEL 的值,从 而保证时钟的可靠性。 |

### DEV\_CLK\_GATE 寄存器(0x08)

| 位域     | 名称                     | 类型  | 复位值 | 描述                  |

|--------|------------------------|-----|-----|---------------------|

| 31: 26 | RESERVED               | R   | 0   | 保留位                 |

| 25     | SARADC0_CL<br>K_GATE   | R/W | 0   | SARADC0_CTRL 模块时钟门控 |

| 24     | RESERVED               | R   | 0   | 保留位                 |

| 23     | IIWDT_CLK_<br>GATE     | R/W | 0   | IIWDT 模块时钟门控        |

| 22: 21 | RESERVED               | R   | 0   | 保留位                 |

| 20     | PWM_PLUS0_<br>CLK_GATE | R/W | 0   | PWM_PLUS0 模块时钟门控    |

| 19: 18 | RESERVED               | R   | 0   | 保留位                 |

| 17     | PWM_BASE0 _CLK_GATE    | R/W | 0   | PWM_BASE0 模块时钟门控    |

| 16     | RESERVED               | R   | 0   | 保留位                 |

| 15     | TIMER_PLUS  0_CLK_GATE | R/W | 0 | TIMER_PLUS0 模块时钟门控 |

|--------|------------------------|-----|---|--------------------|

| 14: 11 | RESERVED               | R   | 0 | 保留位                |

| 10     | SPIO_CLK_GA<br>TE      | R/W | 0 | SPI0 模块时钟门控        |

| 9: 7   | RESERVED               | R   | 0 | 保留位                |

| 6      | UARTO_CLK_<br>GATE     | R/W | 0 | UART0 模块时钟门控       |

| 5      | RESERVED               | R   | 0 | 保留位                |

| 4      | I2C0_CLK_GA<br>TE      | R/W | 0 | I2C0 模块时钟门控        |

| 3: 1   | RESERVED               | R   | 0 | 保留位                |

| 0      | GPIOA_CLK_<br>GATE     | R/W | 0 | GPIOA 模块时钟门控       |

### CHIP\_RST\_ST 寄存器(0x10)

| 位域   | 名称           | 类型  | 复位值 | 描述                                                       |

|------|--------------|-----|-----|----------------------------------------------------------|

| 31:1 | RESERVED     | R   | 0   | 保留位                                                      |

| 0    | IWDT_RST_S T | R/W | 0   | IWDT 复位状态标志寄存器  0:表示没有出现 IWDT 复位  1:表示出现 IWDT 复位  写 1 清零 |

#### RC\_CON 寄存器(0x10)

| 位域    | 名称         | 类型   | 复位值 | 描述                              |

|-------|------------|------|-----|---------------------------------|

| 31:10 | RESERVED   | R    | 0   | 保留位                             |

| 9     | TIMER_SRC_ | D/XX | 0   | 将该为配置为1时,RCLF时钟链接到TIMER_PLUS    |

|       | RCLF_EN    | R/W  |     | 端口的 cntsrc_in[1]端,可用于 RCLF 时钟校准 |

| 8     | TIMER_SRC_ | D/W/ | 0   | 将该为配置为1时,XTAH时钟链接到TIMER_PLUS    |

| 0     | XTAH_EN    | R/W  | O   | 端口的 cntsrc_in[0]端,可用于 RCHF 时钟校准 |

| 7:5   | RESERVED   | R    | 0   | 保留位                             |

|       |            |      |     | RCHF 频率选择控制位                    |

| 4     | RCHF_FSEL  | R/W  | 1   | 0: 48MHz                        |

|       |            |      |     | 1: 24MHz                        |

| 3:2   | RESERVED   | R    | 0   | 保留位                             |

|       |            |      |     | RCLF 使能控制位                      |

| 1     | RCLF_EN    | R/W  | 1   | 0: 关闭 RCLF                      |

|       |            |      |     | 1: 开启 RCLF                      |

|       |            |      |     | RCHF 使能控制位                      |

| 0     | RCHF_EN    | R/W  | 1   | 0: 关闭 RCHF                      |

|       |            |      |     | 1: 开启 RCHF                      |

### XTAL\_CON 寄存器(0x88)

| 位域        | 名称       | 类型 | 复位值   | 描述                         |

|-----------|----------|----|-------|----------------------------|

| 31:1      | RESERVED | R  | 0     | 保留位                        |

|           |          |    |       | XTAL 使能                    |

| 0 XTAL_EN | R/W      | 0  | 0: 关闭 |                            |

|           |          |    | 1: 开启 |                            |

|           |          |    |       | 注: XTAL 使能后,至少需要等待 2ms 再使用 |

### 4.7 PORTCON

## 4.7.1 概述

端口控制模块主要包括引脚输入使能,引脚功能配置,IO 口上拉、下拉、推挽、开漏,引脚唤醒功能,唤醒边沿,驱动电流,上拉电阻可配置。

## 4.7.2 特性

- 配置 IO 口为特定功能

- 支持上拉、下拉、推挽、开漏配置

- 可以配置引脚的输入使能

- 可以配置引脚唤醒使能

- 引脚唤醒边沿可以配置

- 驱动电流可以配置

- 上拉电阻 32K、40K 和 150K 可以配置

## 4.7.3 模块结构框图

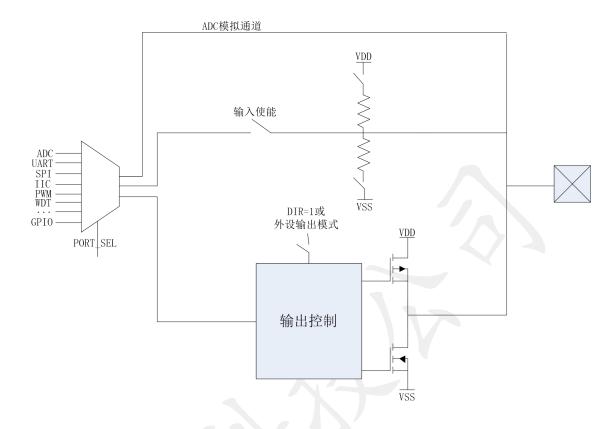

图 5.8.1 PORTCON 模块结构框图

## 4.7.4 功能描述

#### 引脚输入使能

本芯片引脚作为输入或需要输入的外设时,需要打开引脚对应输入使能寄存器(PORTx\_IE),当引脚所在寄存器对应位设置为 1 时,输入使能打开,引脚可获取外部状态。

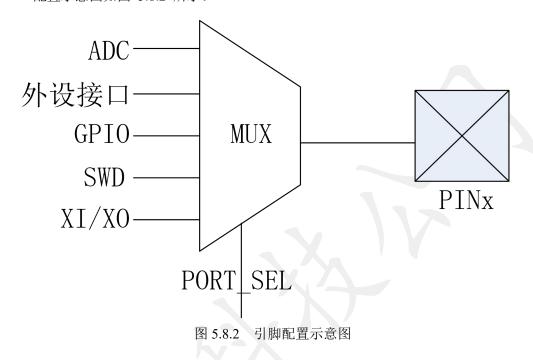

#### 复用功能选择配置

端口复用通过端口复用寄存器 PORTx\_SEL 寄存器实现。当指定位配置为对应值时,引脚功能实现切换。

每个端口可能具备以下功能:

● 通用输入输出接口:引脚作为通用输入输出功能

- 外设接口:将对应引脚切换至指定数字功能,如 TIMER/UART/PWM 等

- 模拟接口:将对应引脚切换至模拟功能,如模数转换器、时钟输入等

- 下载接口: 使用仿真器连接下载程序及单步执行

- 晶振接口:可外接外部高频晶振

配置示意图如图 5.8.2 所示。

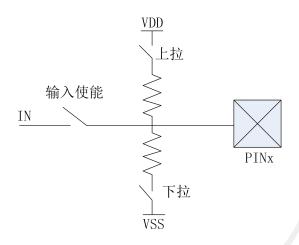

#### 上拉/下拉/推挽/开漏配置

本芯片每个 IO 引脚均可配置为以下模式:

- 上拉输入。

- 下拉输入。

- 推挽输出。

- 开漏输出。

注: 在未配置 PORT 端口状态时,上电默认为浮空状态。

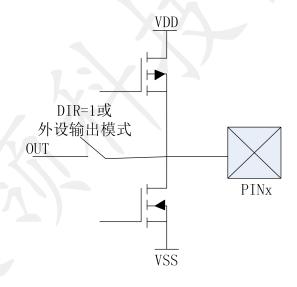

作为输入功能使用时,GPIO DIR 寄存器对应位为 0,该状态为上电默认状态。此时可以开启内部上拉和下拉功能,通过配置 PORTx\_PU 及 PORTx\_PD 寄存器实现,将引脚所对应寄存器指定位配置为 1,即可实现该功能。如图 5.8.3 所示。

图 5.8.3 IO 输入上拉/下拉

作为输出功能使用时,GPIO DIR 寄存器对应位为 1,此时可配置引脚状态为推挽输出或开漏输出,通过配置 PORTx\_OD 寄存器实现。作为推挽输出时,PORTx\_OD 寄存器对应位为 0,芯片具备拉/灌电流的能力,GPIO DATA 寄存器配置值将反映到对应引脚电平。如图 5.8.4 所示。

图 5.8.4 推挽输出

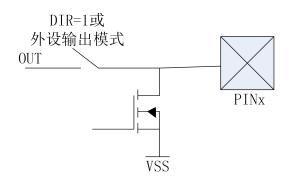

作为开漏输出时,PORTx\_OD 寄存器对应位为 1, 芯片只具备灌电流的能力,不具备拉电流能力。GPIO 输出配置为 0 时,对应引脚将输出 0, 配置为 1 时,输出高阻。若需要输出 1 时,需要将外部引脚接上拉电阻,通过外部上拉实现高电平输出。示意图如图 5.8.5 所示。

图 5.8.5 开漏输出

#### 引脚唤醒功能

引脚可以配置为唤醒功能,可以在低功耗模式下通过引脚进行唤醒操作,唤醒的边沿可以配置为上升沿唤醒或者低电平唤醒。

#### 驱动电流配置

端口的驱动能力可以配置为以下四种模式: 5ma 14ma 22ma 30ma。

#### 上拉电阻配置

上拉电阻可以配置为 32K、40K、150K。

## 4.7.5 寄存器映射

| 名称         | 偏移量                   | 位宽 | 类型  | 复位值 | 描述              |  |  |  |  |

|------------|-----------------------|----|-----|-----|-----------------|--|--|--|--|

| PORT BA    | PORT BASE: 0x400B0000 |    |     |     |                 |  |  |  |  |

| PORTA_SEL0 | 0x00                  | 32 | R/W | 0   | PORTA 功能选择寄存器 0 |  |  |  |  |

| PORTA_SEL1 | 0x04                  | 32 | R/W | 0   | PORTA 功能选择寄存器 1 |  |  |  |  |

| PORTA_IE   | 0x100                 | 32 | R/W | 0   | PORTA 输入使能寄存器   |  |  |  |  |

| PORTA_PU   | 0x200                 | 32 | R/W | 0   | PORTA 上拉使能寄存器   |  |  |  |  |

| PORTA_PD   | 0x300                 | 32 | R/W | 0   | PORTA 下拉使能寄存器   |  |  |  |  |

| PORTA_OD   | 0x400                 | 32 | R/W | 0   | PORTA 开漏使能寄存器   |  |  |  |  |

| PORTA_WKE  | 0x500                 | 32 | R/W | 0   | PORTA 唤醒使能寄存器   |  |  |  |  |

| PORT_CFG   | 0x600                 | 32 | R/W | 0   | PORT 配置寄存器      |  |  |  |  |

## 4.7.6 寄存器描述

### PORTA\_SELO 寄存器(0x00)

| 位域    | 名称     | 类型  | 复位值 | 描述                                                                                                                |

|-------|--------|-----|-----|-------------------------------------------------------------------------------------------------------------------|

| 31:28 | PORTA7 | R/W | 0   | 000: GPIOA7<br>001: IIC0_SCL<br>010: BREAK_IN1<br>011: HALL_IN2<br>111: SARADC_CH5<br>其它: 保留                      |

| 27:24 | PORTA6 | R/W | 0   | 000: GPIOA6<br>001: IIC0_SDA<br>010: 保留<br>011: BREAK_IN0<br>111: SARADC_CH6<br>其它: 保留                            |

| 23:20 | PORTA5 | R/W | 0   | 000: GPIOA5 001: SPI0_SSN 010: TIMERP0_IN1 011: TIMERP0_OUT1 100: PWMB0_CH1 101: PWMP0_CH2 111: SARADC_CH7 其它: 保留 |

| 19:16 | PORTA4 | R/W | 0   | 000: GPIOA4<br>001: IIC0_SCL<br>010: PWMP0_CH1<br>111: XTAH_OUT<br>其它: 保留                                         |

| 15:12 | PORTA3 | R/W | 0   | 000: GPIOA3<br>001: IIC0_SDA<br>010: PWMP0_CH0<br>111: XTAH_IN<br>其它: 保留                                          |

| 11:8 | PORTA2 | R/W | 0 | 000: GPIOA2<br>001: SPI0_MISO<br>010: UART0_RX<br>011: HALL_IN1<br>100: PWMP0_CH2N<br>111: SARADC_CH0<br>其它: 保留 |

|------|--------|-----|---|-----------------------------------------------------------------------------------------------------------------|

| 7:4  | PORTA1 | R/W | 0 | 000: GPIOA1 001: SPI0_MOSI 010: UART0_TX 011: HALL_IN0 100: PWMP0_CH1N 111: SARADC_CH1 其它: 保留                   |

| 3:0  | PORTA0 | R/W | 0 | 000: GPIOA0 001: SPI0_CLK 010: TIMERP0_IN0 011: TIMERP0_OUT0 100: PWMB0_CH0 101: PWMP0_CH0N 其它: 保留              |

### PORTA\_SEL1 寄存器(0x04)

| 位域    | 名称      | 类型  | 复位值 | 描述                                                                                                                    |

|-------|---------|-----|-----|-----------------------------------------------------------------------------------------------------------------------|

| 31:28 | PORTA15 | R/W | 0   | 000: GPIOA15<br>001: SPI0_SSN<br>010: TIMERP0_IN0<br>011: TIMERP0_OUT0<br>100: PWMB0_CH2<br>111: SARADC_CH2<br>其它: 保留 |

| 27:24 | PORTA14 | R/W | 1   | 000: GPIOA14<br>001: SWIO<br>010: TIMERP0_IN1<br>011: TIMERP0_OUT1<br>100: PWMB0_CH1<br>111: SARADC_CH3<br>其它: 保留     |

| 23:20 | PORTA13 | R/W | 1 | 000: GPIOA13<br>001: SWCLK<br>010: PWMP0_CH2<br>其它: 保留                                                                |

|-------|---------|-----|---|-----------------------------------------------------------------------------------------------------------------------|

| 19:16 | PORTA12 | R/W | 0 | 000: GPIOA12<br>001: SPI0_MISO<br>010: TIMERP0_IN0<br>011: TIMERP0_OUT0<br>100: PWMP0_CH1<br>其它: 保留                   |

| 15:12 | PORTA11 | R/W | 0 | 000: GPIOA11<br>001: SPI0_MOSI<br>010: TIMERP0_IN1<br>011: TIMERP0_OUT1<br>100: PWMP0_CH0<br>其它: 保留                   |

| 11:8  | PORTA10 | R/W | 0 | 000: GPIOA10<br>001: SPI0_CLK<br>010: TIMERP0_IN0<br>011: TIMERP0_OUT0<br>100: PWMB0_CH0<br>101: PWMP0_CH2N<br>其它: 保留 |

| 7:4   | PORTA9  | R/W | 0 | 000: GPIOA9 001: UART0_RX 010: TIMERP0_IN1 011: TIMERP0_OUT1 100: PWMB0_CH2 101: PWMP0_CH1N 111: SARADC_CH4 其它: 保留    |

| 3:0   | PORTA8  | R/W | 0 | 000: GPIOA8 001: UART0_TX 010: TIMERP0_IN0 011: TIMERP0_OUT0 100: PWMP0_CH2 101: PWMP0_CH0N 其它: 保留                    |

# PORTA\_IE 寄存器(0x100)

| 位域    | 名称       | 类型  | 复位值   | 描述                         |

|-------|----------|-----|-------|----------------------------|

| 31:16 | RESERVED | R   | 0     | 保留位                        |

| 15:0  | PORTA_IE | R/W | 0x600 | PORTA 输入使能寄存器  0: 禁能 1: 使能 |

#### PORTA\_PU 寄存器(0x200)

| 位域    | 名称       | 类型  | 复位值 | 描述                               |

|-------|----------|-----|-----|----------------------------------|

| 31:16 | RESERVED | R   | 0   | 保留位                              |

|       |          |     |     | PORTA 上拉使能寄存器                    |

| 15:0  | PORTA_PU | R/W | 0   | 0: 禁能 1: 使能                      |

|       |          |     |     | (每个bit 对应1个IO,bit0对应A0,bit1对应A1) |

# PORTA\_PD 寄存器(0x300)

| 位域    | 名称       | 类型  | 复位值 | 描述                                        |

|-------|----------|-----|-----|-------------------------------------------|

| 31:16 | RESERVED | R   | 0   | 保留位                                       |

| 15:0  | PORTA_PD | R/W | 0   | PORTA 下拉使能寄存器<br>0: 禁能 1: 使能              |

|       |          |     |     | (每个 bit 对应 1 个 IO, bit0 对应 A0,bit1 对应 A1) |

# PORTA\_OD 寄存器(0x400)

| 位域    | 名称       | 类型  | 复位值 | 描述                         |  |

|-------|----------|-----|-----|----------------------------|--|

| 31:16 | RESERVED | R   | 0   | 保留位                        |  |

| 15:0  | PORTA_OD | R/W | 0   | PORTA 开漏使能寄存器  0: 禁能 1: 使能 |  |

# PORTA\_WKE 寄存器 (0x500)

| 位域    | 名称        | 类型  | 复位值 | 描述                         |

|-------|-----------|-----|-----|----------------------------|

| 31:16 | RESERVED  | R   | 0   | 保留位                        |

| 15:0  | PORTA_WKE | R/W | 0   | PORTA 唤醒使能寄存器  0: 禁能 1: 使能 |

# PORT\_CFG 寄存器(0x600)

| 位域    | 名称              | 类型  | 复位值 | 描述                          |

|-------|-----------------|-----|-----|-----------------------------|

| 31:12 | RESERVED        | R   | 0   | 保留位                         |

|       |                 |     |     | PORT 唤醒功能选择                 |

| 11    | PORT_WK_RF      | R/W | 0   | 0: 低电平唤醒                    |

|       |                 |     |     | 1: 上升沿唤醒                    |

|       |                 |     |     | PORT 输入迟滞等级选择               |

|       |                 | ,   | XJ  | 0: 低输入迟滞(输入信号大于 0.7VDD 和小于  |

| 10    | 10 PORT_HYS R/W | R/W | 0   | 0.3VDD)                     |

|       | 7               |     |     | 1: 高输入迟滞(输入信号大于 0.85VDD 和小于 |

|       |                 |     |     | 0.15VDD)                    |

|       |                 |     |     | PORT 上拉电阻阻值选择               |

|       |                 |     |     | 00: 保留                      |

| 9:8   | PORT_PUR        | R/W | 10  | 01: 150kΩ                   |

|       |                 |     |     | 10: 40kΩ                    |

|       |                 |     |     | 11: 32kΩ                    |

| 7:4   | RESERVED        | R   | 0   | 保留位                         |

|      |             |     |      | SPIFLASH 的 6 个 PORT 驱动能力选择寄存器 |

|------|-------------|-----|------|-------------------------------|

| DOD! | DODE DO ON  |     |      | 00: 5mA                       |

| 3:2  | PORT_DS_SPI | R/W | 0x10 | 01: 14mA                      |

|      | FLASH       |     |      | 10: 22mA                      |

|      |             |     |      | 11: 30mA                      |

|      |             |     |      | PORT 驱动能力选择寄存器                |

|      | PORT_DS     | R/W | 0x01 | 00: 5mA                       |

| 1:0  |             |     |      | 01: 14mA                      |

|      |             |     |      | 10: 22mA                      |

|      |             |     |      | 11: 30mA                      |

# 4.8 通用 IO(GPIO)

# 4.8.1 概述

通用输入输出模块主要功能包括数据控制、中断控制功能。使用前需使能对应 GPIO 模块时钟。

# 4.8.2 特性

- 最多 16 个独立 IO

- 每个 IO 具有中断入口

- 中断触发条件可配置,支持电平触发和边沿触发

- 电平触发支持高电平和低电平

- 边沿触发支持上升沿、下降沿和双边沿触发

- 每个 IO 均支持上拉、下拉、推挽、开漏功能

# 4.8.3 模块结构框图

# 4.8.4 功能描述

#### 方向控制

除 SWD 引脚外,所有引脚上电后默认状态均为 GPIO 浮空输入(DIR = 0)。 GPIO 方向寄存器(DIRx)用来将每个独立的管脚配置为输入模式或者输出模式:

- 当数据方向设为 0 时,GPIO 对应引脚配置为输入 通过读取相应数据寄存器(DATA)对应位获取指定 GPIO 端口当前状态值

- 当数据方向设为 1 时, GPIO 对应引脚配置为输出

通过向对应端口数据寄存器 (DATA) 对应位写入值改变指定引脚输出, 0 输出低电平, 1 输出高电平。

#### 中断配置和清除

可根据需求将 GPIO 端口对应引脚配置为中断模式,并通过相关寄存器配置中断极性及触发方式。

触发方式分为边沿触发和电平触发两种模式。

- 对于边沿触发中断,可以设置为上升沿触发,下降沿触发或双边沿触发。中断发生 后,标志位具备保持特性,必须通过软件对中断标志位进行清除

- 对于电平触发中断,当外部引脚输入为指定电平时,中断发生。当电平翻转后,中断信号消失,无需软件进行清除。使用电平触发中断,需保证外部信号源保持电平稳定,以便有效中断电平能被端口识别

使用以下寄存器来对产生中断触发方式和极性进行定义:

- GPIO 中断触发方式寄存器 (INTLVLTRG), 用于配置电平触发或边沿触发

- GPIO 中断触发极性寄存器(INTRISEEN),用于配置电平或边沿触发极性

- GPIO 中断边沿触发配置寄存器(INTBE),选择为边沿触发后,用于配置单边沿触发或双边沿触发

通过 GPIO 中断使能寄存器(INTEN)可以使能或者禁止相应端口对应位中断,GPIO 原始中断状态(INTRAWSTAUS)不受使能位影响。当产生中断时,可以在 GPIO 原始中断状态(RAWINTSTAUS)获取中断信号的状态。当中断使能寄存器(INTEN)对应位为 1时,中断状态(INTSTAUS)寄存器可读取到对应中断信号,且中断信号会进入中断配置模块及 NVIC 模块,执行中断程序。

通过写 1 到 GPIO 中断清除寄存器 (INTCLR) 指定位可以清除相应位中断。

# 4.8.5 寄存器映射

| 名称                     | 偏移量  | 位宽         | 类型  | 复位值 | 描述         |  |  |  |

|------------------------|------|------------|-----|-----|------------|--|--|--|

| GPIOA BASE: 0x40060000 |      |            |     |     |            |  |  |  |

| GPIODATA               | 0x00 | GPIO_WIDTH | R/W | 0   | 数据寄存器      |  |  |  |

| GPIODIR                | 0x04 | GPIO_WIDTH | R/W | 0   | 方向设置寄存器    |  |  |  |

| INTLVLTRG              | 0x08 | GPIO_WIDTH | R/W | 0   | 中断检测方式寄存器  |  |  |  |

| INTBE                  | 0x0c | GPIO_WIDTH | R/W | 0   | 沿触发方式寄存器   |  |  |  |

| INTRISEEN              | 0x10 | GPIO_WIDTH | R/W | 0   | 中断事件方式寄存器  |  |  |  |

| INTEN                  | 0x14 | GPIO_WIDTH | R/W | 0   | 中断使能寄存器    |  |  |  |

| INTRAWST<br>AUS        | 0x18 | GPIO_WIDTH | R   | 0   | 中断原始状态寄存器  |  |  |  |

| INTSTAUS               | 0x1c | GPIO_WIDTH | R   | 0   | 中断状态寄存器    |  |  |  |

| INTCLR                 | 0x20 | GPIO_WIDTH | W   | 0   | 沿触发中断清除寄存器 |  |  |  |

GPIOA的 GPIO\_WIDTH为16。

# 4.8.6 寄存器描述

# GPIODATA 寄存器(0x00)

| 位域            | 名称       | 类型  | 复位值 | 描述    |

|---------------|----------|-----|-----|-------|

| 31:GPIO_WIDTH | RESERVED | RO  | 0   | 保留位   |

| GPIO_WIDTH    | GPIODATA | R/W | 0   | 数据寄存器 |

# GPIODIR 寄存器(0x04)

| 位域            | 名称       | 类型  | 复位值 | 描述                                                            |

|---------------|----------|-----|-----|---------------------------------------------------------------|

| 31:GPIO_WIDTH | RESERVED | RO  | 0   | 保留位                                                           |

| GPIO_WIDTH    | GPIODIR  | R/W | 0   | 设置 GPIO 管脚方向:  1: 设置相应位的 GPIO 管脚为输出管脚  0: 设置相应位的 GPIO 管脚为输入管脚 |

## INTLVLTRG 寄存器 (0x08)

| 位域            | 名称        | 类型  | 复位值 | 描述                                                             |

|---------------|-----------|-----|-----|----------------------------------------------------------------|

| 31:GPIO_WIDTH | RESERVED  | RO  | 0   | 保留位                                                            |

| GPIO_WIDTH    | INTLVLTRG | R/W | 0   | 设置 GPIO 管脚中断敏感条件: 1: 设置相应位的 GPIO 管脚为电平检测 0: 设置相应位的 GPIO 管脚为沿检测 |

#### INTBE 寄存器(0x0C)

| 位域            | 名称       | 类型  | 复位值 | 描述                                     |

|---------------|----------|-----|-----|----------------------------------------|

| 31:GPIO_WIDTH | RESERVED | RO  | 0   | 保留位                                    |

| GPIO_WIDTH I  |          |     | 0   | 设置 GPIO 管脚沿触发方式:                       |

|               |          | R/W |     | 1: 设置相应位的 GPIO 管脚为双沿触发中断,即上升沿和下降沿都会触发中 |

|               | INTBE    |     |     | 断                                      |

|               |          |     |     | 0: 设置相应位的 GPIO 管脚为单沿触发                 |

|               |          |     |     | 中断,由 INTRISEEN 寄存器相应位                  |

|               |          |     |     | 确定是上升沿/下降沿触发                           |

# INTRISEEN 寄存器 (0x10)

| 位域            | 名称        | 类型  | 复位值 | 描述                                                                              |

|---------------|-----------|-----|-----|---------------------------------------------------------------------------------|

| 31:GPIO_WIDTH | RESERVED  | RO  | 0   | 保留位                                                                             |

| GPIO_WIDTH    | INTRISEEN | R/W | 0   | 设置 GPIO 管脚中断事件方式:  1: 设置相应位的 GPIO 管脚为上升沿/高电平触发中断  0: 设置相应位的 GPIO 管脚为下降沿/低电平触发中断 |

## INTEN 寄存器(0x14)

| 位域            | 名称       | 类型  | 复位值 | 描述                                                            |

|---------------|----------|-----|-----|---------------------------------------------------------------|

| 31:GPIO_WIDTH | RESERVED | RO  | 0   | 保留位                                                           |

| GPIO_WIDTH    | INTEN    | R/W | 0   | 设置 GPIO 管脚中断使能:  1: 设置相应位的 GPIO 管脚中断使能  0: 设置相应位的 GPIO 管脚中断禁止 |

#### INTRAWSTAUS 寄存器 (0x18)

| 位域            | 名称              | 类型 | 复位值 | 描述                                                                                                  |

|---------------|-----------------|----|-----|-----------------------------------------------------------------------------------------------------|

| 31:GPIO_WIDTH | RESERVED        | RO | 0   | 保留位                                                                                                 |

| GPIO_WIDTH    | INTRAWST<br>AUS | R  | 0   | 当 GPIO 被配置为输入模式时,根据设置的触发条件产生中断标志,不受中断使能寄存器的影响。由硬件置位,软件向GPIOIC写1清除。 1:表示检测到相应位的 GPIO 中断触发条件(原始,掩码之前) |

|               | 1               |    |     | 0:表示没有检测到相应位的 GPIO 中断触发条件                                                                           |

# INTSTAUS 寄存器 (0x1C)

| 位域            | 名称       | 类型 | 复位值 | 描述  |

|---------------|----------|----|-----|-----|

| 31:GPIO_WIDTH | RESERVED | RO | 0   | 保留位 |

|                     |          |   | 0 | 当 GPIO 被配置为输入模式,且相应位的  |

|---------------------|----------|---|---|------------------------|

|                     |          |   |   | 中断被使能时,根据设置的触发条件产生     |

| GPIO_WIDTH INTSTAUS |          |   |   | 中断标志。由硬件置位,软件向 GPIOIC  |

|                     | INTSTAUS | R |   | 写 1 清除。                |

|                     |          |   |   | 1: 表示检测到相应位的 GPIO 管脚产生 |

|                     |          |   |   | 的中断(掩码之后)              |

|                     |          |   |   | 0: 表示没有检测到相应位的 GPIO 管脚 |

|                     |          |   |   | 产生的中断                  |

# INTCLR 寄存器(0x20)

| 位域            | 名称           | 类型 | 复位值 | 描述                                                                                                          |

|---------------|--------------|----|-----|-------------------------------------------------------------------------------------------------------------|

| 31:GPIO_WIDTH | RESER<br>VED | RO | 0   | 保留位                                                                                                         |

| GPIO_WIDTH    | INTCLR       | W  | 0   | 写 1: 清除相应位 GPIO 管脚沿触发中断标志 INTRAWSTAUS 和 INTSTAUS。清除中断标志后,INTCLR 相应位硬件自动恢复为 0。 写 0: 没有影响。 对该寄存器进行读操作,返回值为 0。 |

# 4.9 高级定时器(TIMERPLUS)

# 4.9.1 概述

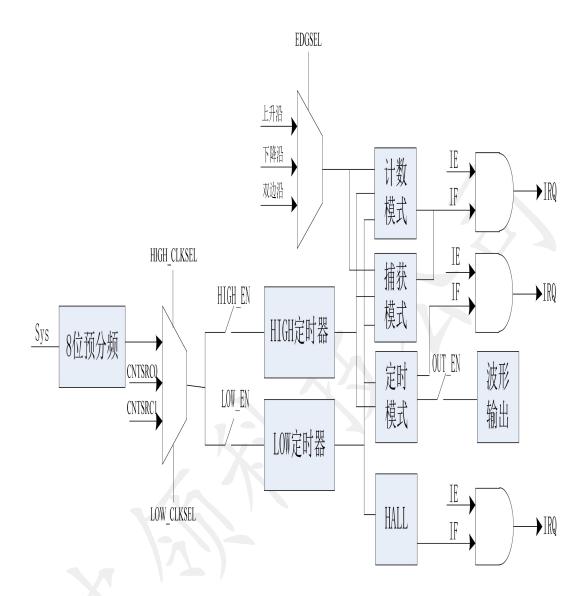

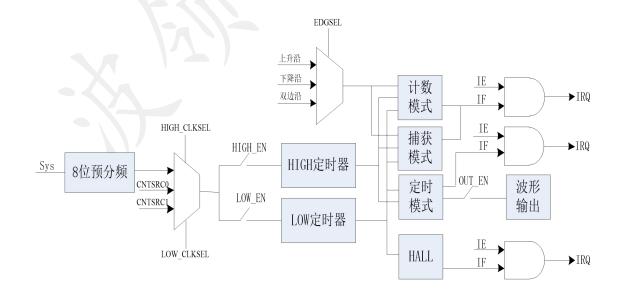

高级定时器模块具备定时、计数、捕捉、HALL、周期脉冲输出等功能,具有一个 8 位 预分频器,支持中断,2 个独立的 16 位的定时器(HIGH 和 LOW),使用前需要使能高级定时器模块时钟。

# 4.9.2 特性

- 2 个独立的 16bit 计数器 (HIGH 和 LOW)

- 8位预分频

- 支持多种中断

- 两个定时器都具有定时、计数、输入捕捉和周期脉冲输出功能

- LOW 计数器支持 HALL 功能

- 支持计数时钟选择

- 两个定时器具有各自的目标值影子寄存器,新的目标值将下周期生效

# 4.9.3 模块结构框图

# 4.9.4 功能描述

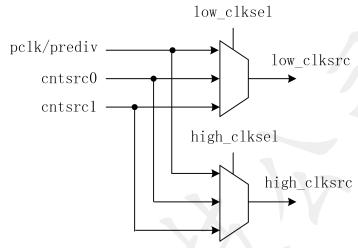

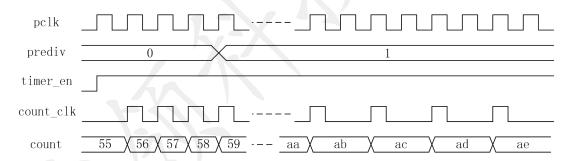

#### 计数时钟源选择与预分频

内部两个定时器都可以分别选择计数时钟源,并且共用一个预分频器。 计数器计数时钟源选择示意图如下:

预分频只用于 pclk, 示意图如下:

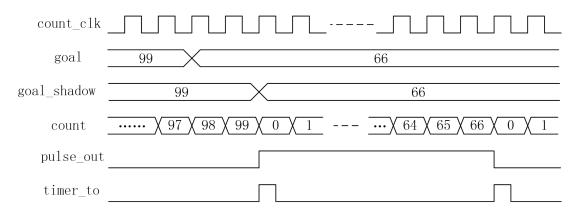

#### 定时模式

基本定时器作为独立的两个 16 位定时器时,向上计数,计数源为系统时钟 Sys。 定时时长 Tout 计算公式如下:

Tout = (Tpre + 1)\*(Tload + 1)/Sys.

注: Tpre 为分频系数, Tload 为装载值的高 16 位或者低 16 位, Sys 为系统时钟。

定时模式下可以配置周期脉冲输出到引脚上,可以作为简单的方波输出。

在定时器工作过程中,修改周期值,不会立即生效,而是在周期结束后下一周期生效。

其中,count\_clk 为计数器的计数时钟,goal 为 CPU 配置的目标值,goal\_shadow 为影子寄存器值,count 为计数值,pulse\_out 为周期脉冲输出的原值,timer\_to 为计数值达到目标值时的标志信号。

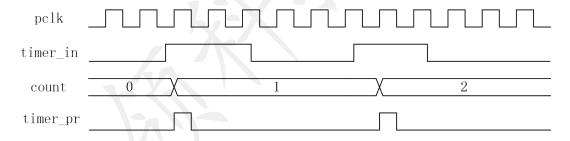

#### 计数模式

定时器配置为计数模式后,计数时钟只能选择 pclk 预分频后的时钟,信号有效沿可以选择上升沿、下降沿、双边沿。

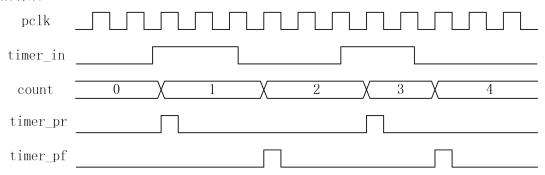

#### 上升沿有效:

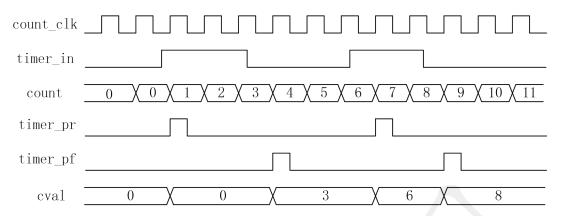

其中计数模式下采用 pclk 为计数器的计数时钟,timer\_in 为外部输入信号,count 为计数值,timer\_pr 为检测到 timer\_in 上升沿标志信号。

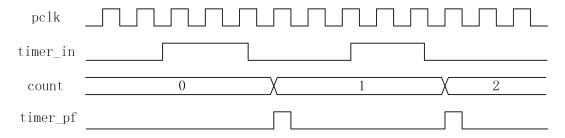

#### 下降沿有效:

其中 pclk 为计数器的计数时钟,timer\_in 为外部输入信号,count 为计数值,timer\_pf 为检测到 timer in 下降沿标志信号。

双沿有效:

其中 pclk 为计数器的计数时钟,timer\_in 为外部输入信号,count 为计数值,timer\_pr 为检测到 timer\_in 上升沿标志信号,timer\_pf 为检测到 timer\_in 下降沿标志信号。

#### 输入捕获模式

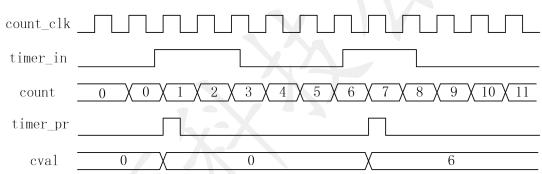

上升沿有效:

其中 count\_clk 为计数器的计数时钟, timer\_in 为外部输入信号, count 为计数值, timer\_pr 为检测到 timer in 上升沿标志信号, cval 为捕获的计数器计数值。

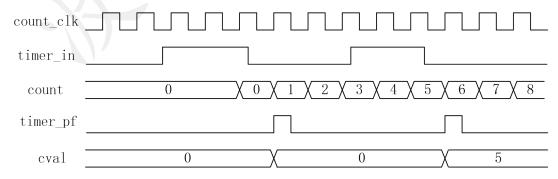

#### 下降沿有效:

其中 count\_clk 为计数器的计数时钟, timer\_in 为外部输入信号, count 为计数值, timer\_pf 为检测到 timer\_in 下降沿标志信号, cval 为捕获的计数器计数值。

#### 双沿有效:

其中 count\_clk 为计数器的计数时钟, timer\_in 为外部输入信号, count 为计数值, timer\_pr 为检测到 timer\_in 上升沿标志信号, timer\_pf 为检测到 timer\_in 下降沿标志信号, cval 为捕获的计数器计数值。

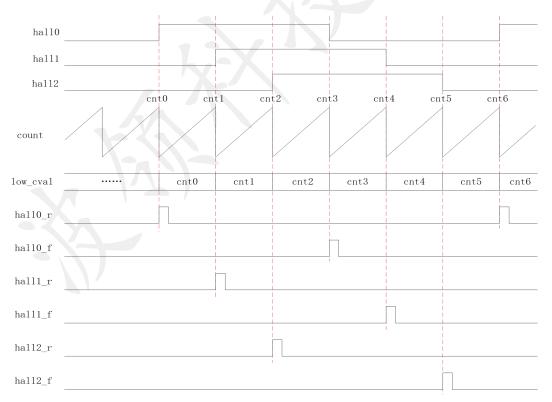

#### HALL 模式

只有 LOW 定时器具有 HALL 模式,可用于霍尔信号采集。

其中 hall0、hall1 和 hall2 为三路输入的 HALL 信号,电路每检测到上升沿和下降沿都会将计数器清零,并且将清零前的计数值保存到 low\_cval 寄存器中,同时会产生各个 HALL 信号的上升沿或下降沿标志信号。

# 4.9.5 寄存器映射

| 名称                         | 偏移量  | 位宽 | 类型  | 复位值 | 描述                      |  |  |

|----------------------------|------|----|-----|-----|-------------------------|--|--|

| TIMERPLUS BASE: 0x40067000 |      |    |     |     |                         |  |  |

| TIMERPLUS_EN               | 0x00 | 32 | R/W | 0   | TIMERPLUS 使能寄存器         |  |  |

| TIMERPLUS_DIV              | 0x04 | 32 | R/W | 0   | TIMERPLUS 计数时钟预分频寄存器    |  |  |

| TIMERPLUS_CTR              | 0x08 | 32 | R/W | 0   | TIMERPLUS 配置寄存器         |  |  |

| TIMERPLUS_IE               | 0x10 | 32 | R/W | 0   | TIMERPLUS 中断使能寄存器       |  |  |

| TIMERPLUS_IF               | 0x14 | 32 | R/W | 0   | TIMERPLUS 中断状态寄存器       |  |  |

| HIGH_GOAL                  | 0x20 | 32 | R/W | 0   | TIMERPLUS HIGH 目标配置寄存器  |  |  |

| HIGH_CNT                   | 0x24 | 32 | R   | 0   | TIMERPLUS HIGH 当前计数值寄存器 |  |  |

| HIGH_CVAL                  | 0x28 | 32 | R   | 0   | TIMERPLUS HIGH 捕获值寄存器   |  |  |

| LOW_GOAL                   | 0x30 | 32 | R/W | 0   | TIMERPLUS LOW 目标配置寄存器   |  |  |

| LOW_CNT                    | 0x34 | 32 | R   | 0   | TIMERPLUS LOW 当前计数值寄存器  |  |  |

| LOW_CVAL                   | 0x38 | 32 | R   | 0   | TIMERPLUS HIGH 捕获值寄存器   |  |  |

| HALL_VAL                   | 0x40 | 32 | R   | 0   | HALL 信号原始值寄存器           |  |  |

# 4.9.6 寄存器描述

# TIMERPLUS\_EN 寄存器(0x00)

| 位域   | 名称         | 类型   | 复位值 | 描述                         |

|------|------------|------|-----|----------------------------|

| 31:2 | RESERVED   | R    | 0   | 保留位                        |

| 1    | TIMERPLUS_ | R/W  | 0   | TIMERPLUS 高 16bit 定时器使能寄存器 |

|      | HIGH_EN    |      |     | 0: 禁能 1: 使能                |

| 0    | TIMERPLUS_ | D/W/ | 0   | TIMERPLUS 低 16bit 定时器使能寄存器 |

|      | LOW_EN     | R/W  | Ŭ   | 0: 禁能 1: 使能                |

# TIMERPLUS\_DIV 寄存器(0x04)

| 位域   | 名称                | 类型  | 复位值 | 描述                                                           |

|------|-------------------|-----|-----|--------------------------------------------------------------|

| 31:8 | RESERVED          | R   | 0   | 保留位                                                          |

| 7: 0 | TIMERPLUS<br>_DIV | R/W | 0   | TIMERPLUS 计数时钟分频寄存器 0x00:表示 1 分频 0x01:表示 2 分频 0xff:表示 256 分频 |

# TIMERPLUS\_CTR 寄存器(0x08)

| 位域    | 名称                | 类型  | 复位值 | 描述                                                                                       |

|-------|-------------------|-----|-----|------------------------------------------------------------------------------------------|

| 31:24 | RESERVED          | R   | 0   | 保留                                                                                       |

| 23    | HIGH_PO_M         | R/W | 0   | TIMER HIGH 周期脉冲输出使能         0: 输出关闭         1: 输出使能                                      |

| 22:21 | HIGH_EXT_<br>EDGE | R/W | 0   | TIMER HIGH 计数模式或输入捕获模式输入信号<br>有效沿选择<br>00: 上升沿有效<br>01: 下降沿有效<br>10: 上升沿或下降沿有效<br>11: 保留 |

| 20    | HIGH_EXT_<br>SEL  | R/W | 0   | TIMER HIGH 计数模式或输入捕获模式输入信号<br>选择<br>0: timer_in0<br>1: timer_in1                         |

| 19:18 | HIGH_CLKS         | R/W | 0   | TIMER HIGH 计数时钟源选择  00: PCLK/PREDIV(选择 pclk 预分频后的时钟)  01: CNTSRC0  10: CNTSRC1  11: 保留   |

| 17:16 | HIGH_MOD<br>E    | R/W | 0 | TIMER HIGH 工作模式寄存器  00: 定时模式(可产生周期脉冲输出信号)  01: 计数模式(计数时钟只能选择 pclk)  10: 输入捕获模式  11: 保留       |

|-------|------------------|-----|---|----------------------------------------------------------------------------------------------|

| 15:8  | RESERVED         | R   | 0 | 保留                                                                                           |

| 7     | LOW_PO_M         | R/W | 0 | TIMER LOW 周期脉冲输出使能 0: 输出关闭 1: 输出使能                                                           |

| 6:5   | LOW_EXT_<br>EDGE | R/W | 0 | TIMER LOW 计数模式或输入捕获模式输入信号<br>有效沿选择<br>00: 上升沿有效<br>01: 下降沿有效<br>10: 上升沿或下降沿有效<br>11: 保留      |

| 4     | LOW_EXT_<br>SEL  | R/W | 0 | TIMER LOW 计数模式或输入捕获模式输入信号<br>选择<br>0: timer_in0<br>1: timer_in1                              |

| 3:2   | LOW_CLKS EL      | R/W | 0 | TIMER LOW 计数时钟源选择  00: PCLK/PREDIV(选择 pclk 预分频后的时钟)  01: CNTSRC0  10: CNTSRC1  11: 保留        |

| 1:0   | LOW_MOD E        | R/W | 0 | TIMER LOW 工作模式寄存器  00: 定时模式 (可产生周期脉冲输出信号)  01: 计数模式 (计数时钟只能选择 pclk)  10: 输入捕获模式  11: HALL 模式 |

# TIMERPLUS\_IE 寄存器(0x10)

| 位域    | 名称         | 类型  | 复位值 | 描述            |

|-------|------------|-----|-----|---------------|

| 31:22 | RESERVED   | R   | 0   | 保留位           |

| 21    | HALL2_F_IE | R/W | 0   | HALL2 下降沿中断使能 |

| 20    | HALL2_R_IE  | R/W | 0 | HALL2 上升沿中断使能              |

|-------|-------------|-----|---|----------------------------|

| 19    | HALL1_F_IE  | R/W | 0 | HALL1 下降沿中断使能              |

| 18    | HALL1_R_IE  | R/W | 0 | HALL1 上升沿中断使能              |

| 17    | HALLO_F_IE  | R/W | 0 | HALL0 下降沿中断使能              |

| 16    | HALLO_R_IE  | R/W | 0 | HALL0 上升沿中断使能              |

| 15:11 | RESERVED    | R   | 0 | 保留位                        |

| 10    | HIGH_PF_IE  | R/W | 0 | TIMERPLUS HIGH 输入脉冲下降沿中断使能 |

| 9     | HIGH _PR_IE | R/W | 0 | TIMERPLUS HIGH 输入脉冲上升沿中断使能 |

| 8     | HIGH _TO_IE | R/W | 0 | TIMERPLUS HIGH 达到目标值中断使能   |

| 7:3   | RESERVED    | R   | 0 | 保留位                        |

| 2     | LOW_PF_IE   | R/W | 0 | TIMERPLUS LOW 输入脉冲下降沿中断使能  |

| 1     | LOW_PR_IE   | R/W | 0 | TIMERPLUS LOW 输入脉冲上升沿中断使能  |

| 0     | LOW_TO_IE   | R/W | 0 | TIMERPLUS LOW 达到目标值中断使能    |

# TIMERPLUS\_IF 寄存器(0x14)

| 位域    | 名称          | 类型  | 复位值 | 描述            |

|-------|-------------|-----|-----|---------------|

| 31:22 | RESERVED    | R   | 0   | 保留位           |

| 21    | HALL2 F IF  | R/W | 0   | HALL2 下降沿中断状态 |

|       | 1.0002      | K/W | 0   | 写 1 清零        |

| 20    | HALLO D. IE | R/W | 0   | HALL2 上升沿中断状态 |

|       | HALL2_R_ IF | K/W |     | 写 1 清零        |

| 19    | HALL1 E IE  | R/W | 0   | HALL1 下降沿中断状态 |

|       | HALL1_F_ IF | K/W | · · | 写 1 清零        |

| 18    | HALL1 R IF  | R/W | 0   | HALL1 上升沿中断状态 |

|       |             |     |     | 写1清零          |

| 17    | HALL0 F IF  | R/W | 0   | HALL0 下降沿中断状态 |

|       |             |     |     | 写1清零          |

| 16    | HALL0_R_IF   | R/W | 0 | HALL0 上升沿中断状态<br>写 1 清零               |

|-------|--------------|-----|---|---------------------------------------|

| 15:11 | RESERVED     | R   | 0 | 保留位                                   |

| 10    | HIGH _PF_ IF | R/W | 0 | TIMERPLUS HIGH 输入脉冲下降沿中断<br>状态 写 1 清零 |

| 9     | HIGH _PR_ IF | R/W | 0 | TIMERPLUS HIGH 输入脉冲上升沿中断<br>状态 写 1 清零 |

| 8     | HIGH _TO_ IF | R/W | 0 | TIMERPLUS HIGH 达到目标值中断状态<br>写 1 清零    |

| 7:3   | RESERVED     | R   | 0 | 保留位                                   |

| 2     | LOW_PF_IF    | R/W | 0 | TIMERPLUS LOW 输入脉冲下降沿中断状态 写 1 清零      |

| 1     | LOW_PR_IF    | R/W | 0 | TIMERPLUS LOW 输入脉冲上升沿中断状态 写 1 清零      |

| 0     | LOW_TO_IF    | R/W | 0 | TIMERPLUS LOW 达到目标值中断状态<br>写 1 清零     |

# TIMERPLUS\_HIGH\_LOAD 寄存器(0x20)

| 位域    | 名称        | 类型  | 复位值 | 描述                         |

|-------|-----------|-----|-----|----------------------------|

| 31:16 | RESERVED  | R   | 0   | 保留位                        |

|       |           |     |     | TIMERPLUS HIGH 定时器目标配置寄存器  |

| 15:0  | HIGH_LOAD | R/W | 0   | 当高 16bit 计数器向上计数达到该设定值后,会产 |

|       |           |     |     | 生相应状态信号                    |

# TIMERPLUS\_HIGH\_CNT 寄存器(0x24)

| 位域    | 名称       | 类型 | 复位值 | 描述                      |

|-------|----------|----|-----|-------------------------|

| 31:16 | RESERVED | R  | 0   | 保留位                     |

| 15:0  | HIGH_CNT | R  | 0   | TIMERPLUS HIGH 定时器当前计数值 |

# TIMERPLUS\_HIGH\_CVAL 寄存器(0x28)

| 位域    | 名称        | 类型 | 复位值 | 描述                    |

|-------|-----------|----|-----|-----------------------|

| 31:16 | RESERVED  | R  | 0   | 保留位                   |

| 15:0  | HIGH_CVAL | R  | 0   | TIMERPLUS HIGH 捕获值计数值 |

#### TIMERPLUS\_LOW\_LOAD 寄存器(0x30)

| 位域    | 名称       | 类型  | 复位值 | 描述                         |

|-------|----------|-----|-----|----------------------------|

| 31:16 | RESERVED | R   | 0   | 保留位                        |

|       |          |     |     | TIMERPLUS LOW 定时器目标配置寄存器   |

| 15:0  | LOW_LOAD | R/W | 0   | 当低 16bit 计数器向上计数达到该设定值后,会产 |

|       |          |     |     | 生相应状态信号                    |

# TIMERPLUS\_LOW\_CNT 寄存器(0x34)

| 位域    | 名称       | 类型 | 复位值 | 描述                     |

|-------|----------|----|-----|------------------------|

| 31:16 | RESERVED | R  | 0   | 保留位                    |

| 15:0  | LOW_CNT  | R  | 0   | TIMERPLUS LOW 定时器当前计数值 |

## TIMERPLUS\_LOW\_CVAL 寄存器(0x38)

| 位域    | 名称       | 类型 | 复位值 | 描述                   |

|-------|----------|----|-----|----------------------|

| 31:16 | RESERVED | R  | 0   | 保留位                  |

| 15:0  | LOW_CVAL | R  | 0   | TIMERPLUS LOW 捕获值计数值 |

# HALL\_VAL 寄存器描述(0x40)

| 位域   | 名称       | 类型 | 复位值 | 描述  |

|------|----------|----|-----|-----|

| 31:3 | RESERVED | R  | 0   | 保留位 |

| 2 | HALL2_VAL | R | 0 | HALL2 的原始信号电平 |

|---|-----------|---|---|---------------|

| 1 | HALL1_VAL | R | 0 | HALL1 的原始信号电平 |

| 0 | HALL0_VAL | R | 0 | HALL0 的原始信号电平 |

# 4.10 独立看门狗时钟(IWDT)

# 4.10.1 概述

独立看门狗定时器(IWDT)主要用于控制程序流程正确,在程序流长时间未按既定流程执行指定程序的情况下复位芯片。使用前需使能对应 IWDT 模块时钟。

# 4.10.2 特性

- 产生计数器溢出复位信号,复位信号使能可配

- 具有 32 位计数位宽,可配置灵活、宽范围的溢出周期

- 具有中断功能

- 具有喂狗功能

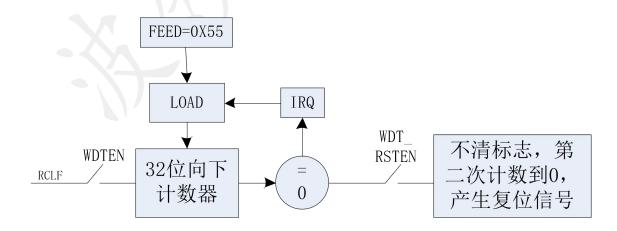

# 4.10.3 模块结构框图

# 4.10.4 功能描述

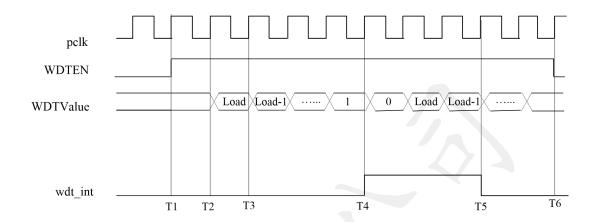

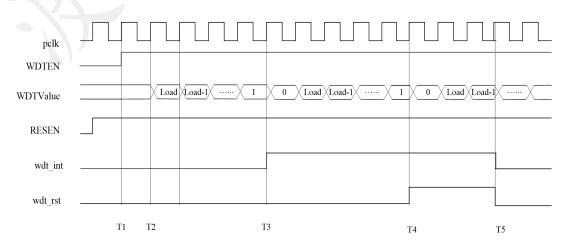

#### 中断模式

- 1)软件首先设置计数初值和参数,之后启动 IWDT 计数(T1 时刻, IWDTEN 有效)。

- 2) IWDTEN 有效后,在 pclk 上升沿(T2 时刻),装载初值。开始递减计数,每一个pclk 时钟沿减 1,计数值为 0(T4 时刻)后继续重置为 Load 后计数。

- 3) T4 时刻,当 IWDTValue 递减为 0 时,IWDTIS 寄存器的 Watchdog Interrupt 位被硬件置 1,向系统输出 IWDT int 中断信号。

- 4) CPU 接收到 IWDT int 中断后,进行中断处理,软件清除中断(T5时刻)。

- 5) 软件设置 IWDTEN 为 0 (T6 时刻),则停止计数。

#### 复位模式

1)软件首先设置计数初值和参数,之后启动 IWDT 计数(T1 时刻, IWDTEN 有效)。

- 2) IWDTEN 有效后,在 pclk 上升沿(T2 时刻),装载初值。开始递减计数,每一个 pclk 时钟沿减 1,计数值为 0(T3 时刻)后继续重置为 Load 后计数。

- 3) T3 时刻,当 IWDTValue 递减为 0 时,IWDTIS 寄存器的 Watchdog Interrupt 位被硬件置 1,向系统输出 IWDT int 中断信号。

- 4) IWDT\_int 中断信号产生(T3 时刻)后,如果一直没有得到响应,那么当 IWDTValue 再次计数到 0(T4 时刻),如果 IWDTControl 寄存器中 RSTEN 位为 1 时(图中所示),IWDT\_rst 信号有效,否则当 RSTEN 为 0 时,IWDT\_rst 信号无效。IWDT\_rst 有效时可用于产生系统复位。

- 5) 如果 IWDT\_rst 信号产生后,未发生系统复位,则通过清除 IWDT 中断标志,可以清除 IWDT rst 信号, 如图所示 T5 时刻 CPU 清中断, IWDT int 和 IWDT rst 信号同时无效。

# 4.10.5 寄存器映射

| 名称                    | 偏移量  | 位宽 | 类型  | 复位值 | 描述            |  |  |  |

|-----------------------|------|----|-----|-----|---------------|--|--|--|

| IWDT BASE: 0x4006A000 |      |    |     |     |               |  |  |  |

| IWDTLOAD              | 0x00 | 32 | R/W | 0   | IWDT 初值寄存器    |  |  |  |

| IWDTVALUE             | 0x04 | 32 | R   | 0   | IWDT 当前计数值寄存器 |  |  |  |

| IWDTCTRL              | 0x08 | 32 | R/W | 0   | IWDT 控制寄存器    |  |  |  |

| IWDTIF                | 0x0C | 32 | R/W | 0   | IWDT 中断状态寄存器  |  |  |  |

| IWDTFEED              | 0x10 | 32 | R/W | 0   | IWDT 喂狗寄存器    |  |  |  |

# 4.10.6 寄存器描述

# IWDTLOAD 寄存器 (0x00)

| 位域   | 名称       | 类型  | 复位值 | 描述                           |

|------|----------|-----|-----|------------------------------|

|      |          |     |     | 包含 IWDT 计数器的初始值。             |

|      |          |     |     | IWDT 启动时,计数器自动装载 IWDTLOAD 值, |

|      |          |     |     | 开始递减计数。当计数器值计到0时,产生中         |

| 31:0 | IWDTLOAD | R/W | 0   | 断,将 IWDTLOAD 寄存器中的值再次装载到计数   |

|      |          |     |     | 器中,继续计数。再次计数到0时,如果中断         |

|      |          |     |     | 状态未清除,则会产生复位。                |

|      |          |     |     | IWDT 启动后设置 IWDTLOAD 寄存器无效。   |

#### IWDTVALUE 寄存器(0x04)

| 位域   | 名称        | 类型      | 复位值 | 描述                    |

|------|-----------|---------|-----|-----------------------|

| 31:0 | IWDTVALUE | VALUE R |     | 该寄存器为只读寄存器,复位值为0。读该寄存 |

| 31.0 | IWDIVALUE |         | U   | 器时,返回计数器的当前计数值。       |

# IWDTCTRL 寄存器(0x08)

| 位域   | 名称       | 类型  | 复位值 | 描述           |

|------|----------|-----|-----|--------------|

| 31:2 | RESERVED | RO  | 0   | 保留位          |

|      |          |     |     | IWDT 复位输出使能位 |

| 1    | RSTEN    | R/W | 0   | 1: 使能复位      |

|      |          |     |     | 0: 禁止复位      |

|      |          |     |     | IWDT 启动位     |

| 0    | IWDTEN   | R/W | 0   | 1:启动 IWDT 计数 |

|      |          |     |     | 0: 停止计数      |

#### IWDTIF 寄存器 (0x0C)

| 位域   | 名称          | 类型   | 复位值 | 描述               |

|------|-------------|------|-----|------------------|

| 31:1 | RESERVED    | RO   | 0   | 保留位              |

|      | 0 IWDT_IF R | D/W/ | 0   | IWDT 中断状态位,高有效   |

| U    |             | R/W  |     | 硬件置位,软件写0清除,写1无效 |

#### IWDTFEED 寄存器 (0x10)

| 位域   | 名称       | 类型  | 复位值 | 描述                         |

|------|----------|-----|-----|----------------------------|

| 31:8 | RESERVED | RO  | 0   | 保留位                        |

|      |          |     |     | IWDT 重启计数器寄存器              |

| 7:0  | FEED     | R/W | 0   | 向该寄存器写入 0x55 后会重启 IWDT 计数器 |

|      |          |     |     | (喂狗操作)                     |

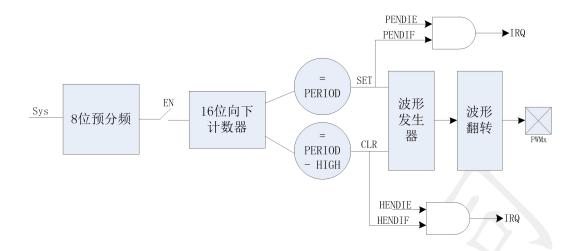

# 4.11 基本脉冲宽度调制发生器(PWMBASE)

# 4.11.1 概述

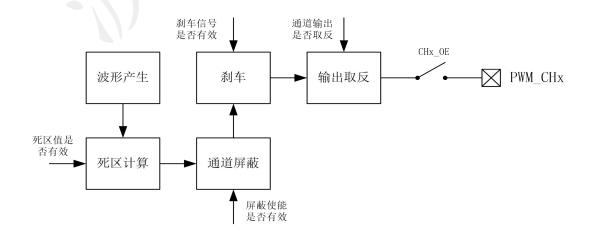

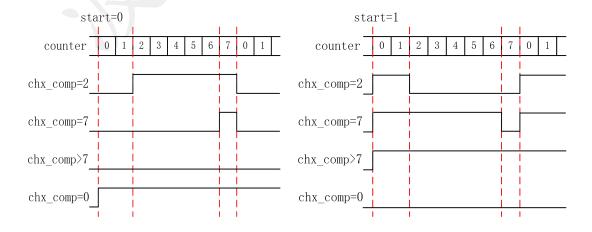

PWMBASE 模块提供 3 路(CH0、CH1、CH2)独立通道,支持预分频功能,支持输出电平翻转,支持到达翻转点中断和周期结束中断。使用 PWMBASE 模块之前需要使能 PWMBASE 时钟。

# 4.11.2特性

- 3个 16bit PWM,可输出不同占空比的 PWM 波形

- 8bit 预分频计数器

- 输出电平翻转

- 支持到达翻转点中断和周期结束中断

# 4.11.3 模块结构框图

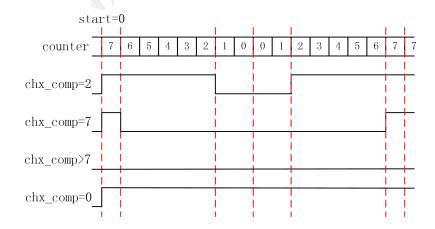

# 4.11.4 功能描述

#### 使用流程

- PWMBASE 时钟使能

- PORT 端口配置为 PWMBASE 功能

- 配置预分频(PWMBASE\_DIV)寄存器

- 配置输出翻转(PWMBASE CON)寄存器

- 配置中断使能(PWMBASE\_INT\_EN)寄存器

- 配置周期(PWMBASEx\_PERIOD)和翻转点(PWMBASEx\_CHx\_COMP)寄存器

- 如果配置了中断,使能 PWMBASE 中断

- 配置波形输出使能(PWMBASE CON)寄存器

- 配置 PWMBASE 使能位(PWMBASE\_EN),开启 PWMBASE

# 4.11.5 寄存器映射

| 名称                   | 偏移量      | 位宽               | 类型  | 复位值 | 描述                    |  |  |  |  |

|----------------------|----------|------------------|-----|-----|-----------------------|--|--|--|--|

| PWMBASE              | BASE: 02 | BASE: 0x400B1000 |     |     |                       |  |  |  |  |

| PWMBASE_EN           | 0x00     | 32               | R/W | 0   | PWMBASE 使能寄存器         |  |  |  |  |

| PWMBASE_DIV          | 0x04     | 32               | R/W | 0   | PWMBASE 时钟预分频寄存器      |  |  |  |  |

| PWMBASE_CON          | 0x08     | 32               | R/W | 0   | PWMBASE 输出配置寄存器       |  |  |  |  |

| PWMBASE_PERI<br>OD   | 0x0C     | 32               | R/W | 0   | PWMBASE 周期配置寄存器       |  |  |  |  |

| PWMBASE_IE           | 0x10     | 32               | R/W | 0   | PWMBASE 中断使能寄存器       |  |  |  |  |

| PWMBASE_IF           | 0x14     | 32               | R/W | 0   | PWMBASE 中断状态寄存器       |  |  |  |  |

| PWMBASE_CNT          | 0x18     | 32               | R/W | 0   | PWMBASE 当前计数值寄存器      |  |  |  |  |

| PWMBASE_CH0_<br>COMP | 0x20     | 32               | R/W | 0   | PWMBASE 通道 0 翻转点配置寄存器 |  |  |  |  |

| PWMBASE_CH1_<br>COMP | 0x30     | 32               | R/W | 0   | PWMBASE 通道 1 翻转点配置寄存器 |  |  |  |  |

| PWMBASE_CH2_<br>COMP | 0x40     | 32               | R/W | 0   | PWMBASE 通道 2 翻转点配置寄存器 |  |  |  |  |

# 4.11.6寄存器描述

# PWMBASE\_EN 寄存器(0x00)

| 位域   | 名称             | 类型  | 复位值 | 描述                                                                                                                                                        |

|------|----------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:1 | RESERVED       | R   | 0   | 保留位                                                                                                                                                       |

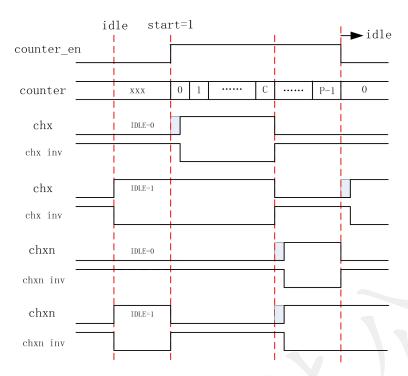

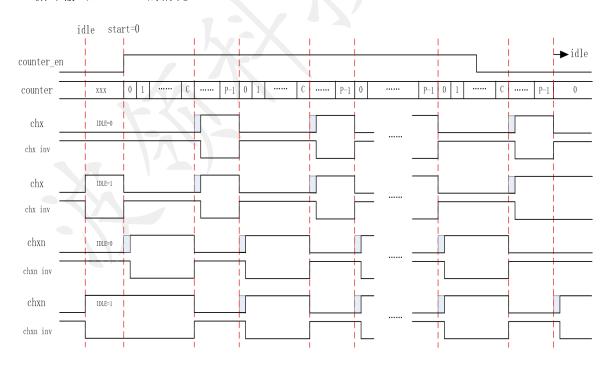

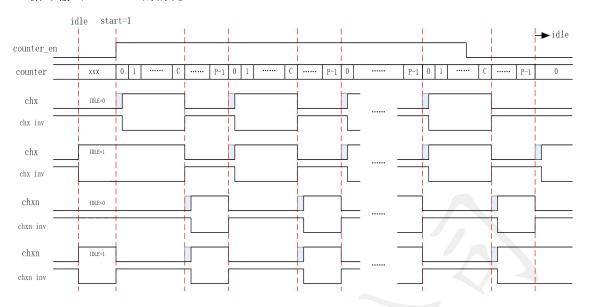

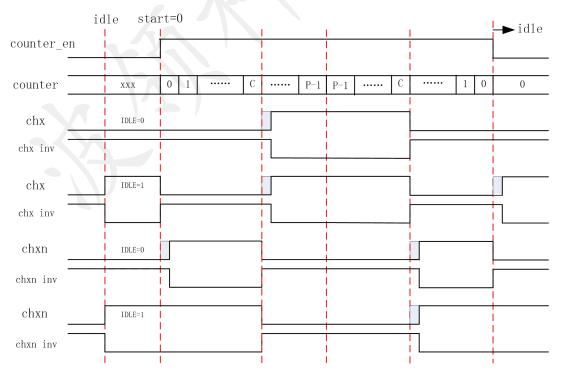

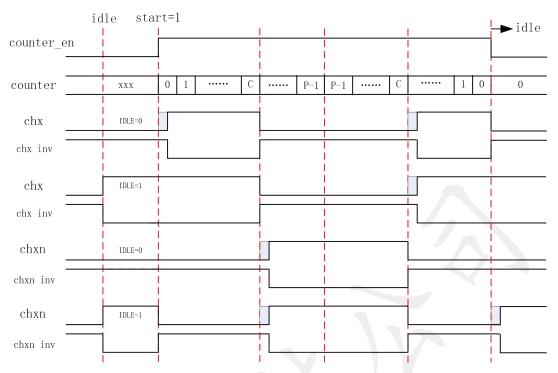

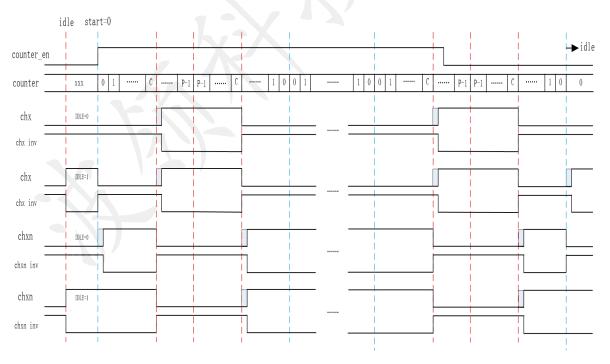

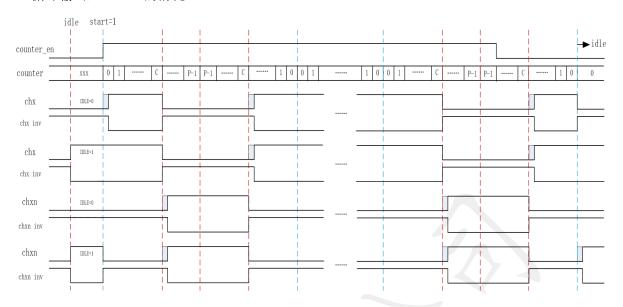

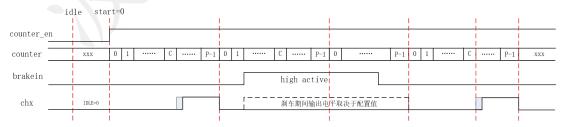

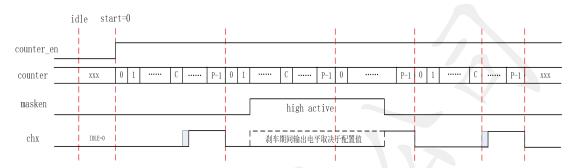

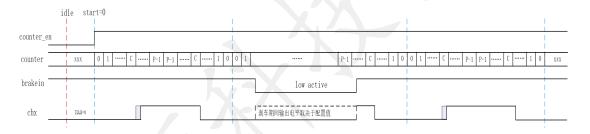

| 0    | COUNTER_<br>EN | R/W | 0   | PWMBASE 计数器使能寄存器<br>当该位配置为 1,则表示计数器开始计数,<br>CH0/CH1/CH2 按照事先配置好的周期值、比较值<br>产生相应通道的 PWM 输出波形。<br>当该位配置为 0,则表示停止计数器计数,当计满<br>一个完整计数周期后输出波形电平恢复到初始 0<br>电平状态 |

# PWMBASE\_DIV 寄存器 (0x04)

| 位域   | 名称              | 类型  | 复位值 | 描述                                                                       |  |

|------|-----------------|-----|-----|--------------------------------------------------------------------------|--|

| 31:8 | RESERVED        | R   | 0   | 保留位                                                                      |  |

| 7: 0 | PWMBASE<br>_DIV | R/W | 0   | PWMBASE 计数时钟预分频寄存器 0x00:表示 1 分频 0x01:表示 2 分频 0x02:表示 3 分频 0xff:表示 256 分频 |  |

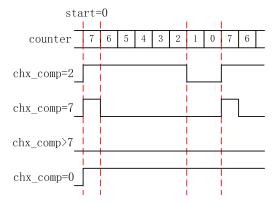

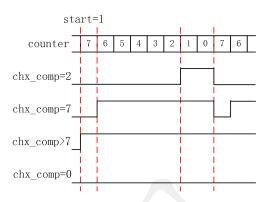

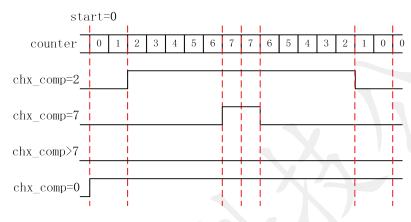

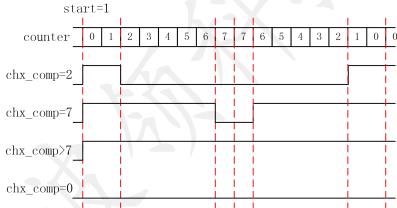

## PWM\_CON 寄存器(0x08)

| 位域   | 名称          | 类型  | 复位值 | 描述                                                               |

|------|-------------|-----|-----|------------------------------------------------------------------|

| 31:7 | RESERVED    | R   | 0   | 保留位                                                              |

| 6    | CH2_OE      | R/W | 0   | CH2 通道波形输出使能<br>0:输出关闭,管脚上为高阻状态<br>1:输出 CH2 方波                   |

| 5    | CH1_OE      | R/W | 0   | CH1 通道波形输出使能<br>0:输出关闭,管脚上为高阻状态<br>1:输出 CH1 方波                   |

| 4    | СН0_ОЕ      | R/W | 0   | CH0 通道波形输出使能<br>0:输出关闭,管脚上为高阻状态<br>1:输出 CH0 方波                   |

| 3    | REVERSED    | RO  | 0   | 保留位                                                              |

| 2    | CH2_OUT_INV | R/W | 0   | CH2 输出极性是否翻转寄存器  0: 不改变, CH2 输出波形为原始波形  1: 极性翻转, CH2 输出波形为原始波形翻转 |

| 1    | CH1_OUT_INV | R/W | 0   | CH1 输出极性是否翻转寄存器  0: 不改变, CH1 输出波形为原始波形  1: 极性翻转, CH1 输出波形为原始波形翻转 |

| 0    | CH0_OUT_INV | R/W | 0   | CH0 输出极性是否翻转寄存器  0: 不改变, CH0 输出波形为原始波形  1: 极性翻转, CH0 输出波形为原始波形翻转 |

# PWMBASE\_PERIOD 寄存器(0x0C)

| 位域    | 名称          | 类型  | 复位值    | 描述                                                                                             |

|-------|-------------|-----|--------|------------------------------------------------------------------------------------------------|